# **ADC Driver Evaluation Boards**

National Semiconductor Application Note 1812 Jason Seitz and Maithil Pachchigar March 6, 2008

## **General Description**

The ADC driver evaluation boards are designed to aid in the characterization of National Semiconductor's high-speed operational amplifier portfolio. Utilize these evaluation boards as guides for high frequency layout and as tools to aid in the design of ADC driver applications.

| ADC Driver                   | Package     | Device       |

|------------------------------|-------------|--------------|

| Configuration                |             |              |

| Single to Single             | 6-Pin SOT23 | LMH6611MK or |

|                              |             | LMH6618MK    |

| Single to Differential       | 8-Pin SOIC  | LMH6612MA or |

|                              |             | LMH6619MA    |

| Differential to Differential | 8-Pin SOIC  | LMH6612MA or |

|                              |             | LMH6619MA    |

Although specifically designed for high speed op amps, these evaluation boards can be used for op amps in these packages with the same pinout.

## **Basic Operation**

### Single to Single ADC Driver

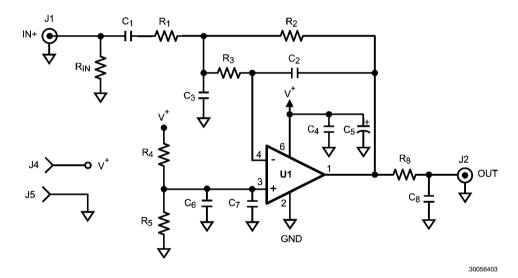

This architecture has a single-ended input source connected to the input of the op amp and the single-ended output of the op amp can then be fed off board to the single-ended input of an ADC. Figure 1 shows the board schematic of the single to single ADC driver in a 2nd order multiple-feedback inverting configuration. The inverting configuration is preferred over the non-inverting configuration, as it offers more linear output response. The ADC driver's cutoff frequency is found from the equation:

$$f_0 = \frac{1}{2\pi} * \sqrt{\frac{1}{R_2 * R_3 * C_2 * C_3}}$$

The op amp's gain is set by the equation:

$$GAIN = -\frac{R_2}{R_1}$$

FIGURE 1. Single to Single ADC Driver Board Schematic

A sample Bill of Material (BOM) for a single to single ADC driver board is given in the table below. The ADC driver will have a cutoff frequency of 500 kHz and a gain of -1.

| Designator                      | Description        | Comment         |  |

|---------------------------------|--------------------|-----------------|--|

| C <sub>1</sub>                  | 0805 Capacitor     | 1 μF            |  |

| C <sub>2</sub>                  | 0805 Capacitor     | 150 pF          |  |

| C <sub>3</sub>                  | 0805 Capacitor     | 1 nF            |  |

| C <sub>4</sub>                  | 0603 Capacitor     | 0.1 μF          |  |

| C <sub>5</sub>                  | Tantalum Capacitor | 6.8 μF          |  |

| C <sub>6</sub>                  | 0805 Capacitor     | 5.6 μF          |  |

| C <sub>7</sub>                  | 0805 Capacitor     | 0.1 μF          |  |

| C <sub>8</sub>                  | 0805 Capacitor     | 220 pF          |  |

| J1                              | SMA Connector      | IN+             |  |

| J2                              | SMA Connector      | OUT             |  |

| J4, J5                          | Test Point         | Test Point      |  |

| R <sub>1</sub> , R <sub>2</sub> | 0805 Capacitor     | 549             |  |

| $R_3$                           | 0805 Capacitor     | 1.24k           |  |

| R <sub>4</sub> , R <sub>5</sub> | 0805 Capacitor     | 14.3k           |  |

| R <sub>8</sub>                  | 0805 Capacitor     | 22              |  |

| R <sub>IN</sub>                 | 0805 Capacitor     | 50              |  |

| U1                              | 6-Pin SOT23        | LMH6611/LMH6618 |  |

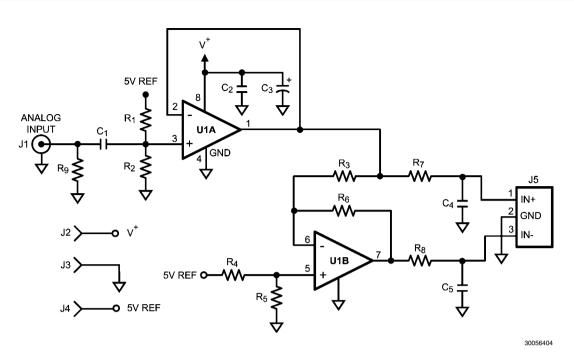

#### Single to Differential ADC Driver

The single to differential ADC driver board schematic in Figure 2 utilizes a dual op amp to buffer a single-ended source to drive an ADC with differential inputs. One of the op amps, U1A, is configured as a unity gain buffer that drives the inverting (IN–) input of the op amp U1B and the non-inverting (IN+) input of the ADC. U1B inverts the input signal and drives the inverting input of the ADC. The ADC driver is configured for a gain of +2 to reduce the noise without sacrificing THD performance. The common mode voltage of 2.5V is supplied at the non-inverting inputs of both op amps U1A and U1B. This configuration produces differential  $\pm 2.5~V_{PP}$  output sig-

nals, when the single-ended input signal of 0 to VREF is AC coupled into the non-inverting terminal of the op amp and each non-inverting terminal of the op amp is biased at the midscale of 2.5V. The two output RC anti-aliasing filters are used between the outputs of both U1A and U1B and the inputs of the ADC to minimize the effect of undesired high frequency noise coming from the input source. Each RC filter's cutoff frequency is found from the equation:

$$\int_0 = \frac{1}{2\pi RC}$$

FIGURE 2. Single to Differential ADC Driver Board Schematic

A sample Bill of Material (BOM) for a single to differential ADC driver board is given in the table below.

| Designator                                                        | Description        | Comment         |  |

|-------------------------------------------------------------------|--------------------|-----------------|--|

| C <sub>1</sub>                                                    | 0805 Capacitor     | 10 μF           |  |

| C <sub>2</sub>                                                    | 0805 Capacitor     | 0.1 μF          |  |

| C <sub>3</sub>                                                    | Tantalum Capacitor | 6.8 μF          |  |

| C <sub>4</sub> , C <sub>5</sub>                                   | 0805 Capacitor     | 220 pF          |  |

| J1                                                                | SMA Connector      | Analog Input    |  |

| J2, J3, J4                                                        | Test Point         | Test Point      |  |

| J5                                                                | SIP3               | Out             |  |

| R <sub>1</sub> , R <sub>2</sub> , R <sub>4</sub> , R <sub>5</sub> | 0805 Capacitor     | 2.5k            |  |

| R <sub>3</sub> , R <sub>6</sub>                                   | 0805 Capacitor     | 560             |  |

| R <sub>7</sub> , R <sub>8</sub>                                   | 0805 Capacitor     | 33              |  |

| R <sub>9</sub>                                                    | 0805 Capacitor     | 50              |  |

| U1                                                                | 8-Pin SOIC         | LMH6612/LMH6619 |  |

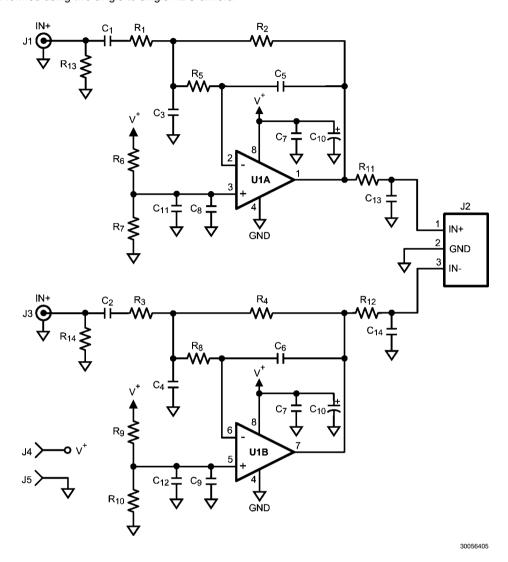

### **Differential to Differential ADC Driver**

A dual op amp can be configured as a differential to differential ADC driver to buffer a differential source to a differential input ADC as shown in *Figure 3*. The differential to differential ADC driver can be formed using two single to single ADC drivers.

Each output from these drivers goes to a separate input of the differential ADC. Each single to single ADC driver uses the same components and is in a multi-feedback inverting configuration.

FIGURE 3. Differential to Differential ADC Driver Board Schematic

A sample Bill of Material (BOM) for a differential to differential ADC driver board is given in the table below. The ADC driver will have a cutoff frequency of 500 kHz and a gain of -1.

| Designator                                                         | Description        | Comment         |  |

|--------------------------------------------------------------------|--------------------|-----------------|--|

| $C_1, C_2$                                                         | 0805 Capacitor     | 1 μF            |  |

| C <sub>3</sub> , C <sub>4</sub>                                    | 0805 Capacitor     | 1 nF            |  |

| C <sub>5</sub> , C <sub>6</sub>                                    | 0603 Capacitor     | 150 pF          |  |

| C <sub>7</sub> , C <sub>8</sub> , C <sub>9</sub>                   | 0805 Capacitor     | 0.1 μF          |  |

| C <sub>10</sub>                                                    | Tantalum Capacitor | 6.8 µF          |  |

| C <sub>11</sub> , C <sub>12</sub>                                  | 0805 Capacitor     | 5.6 μF          |  |

| C <sub>13</sub> , C <sub>14</sub>                                  | 0805 Capacitor     | 220 pF          |  |

| J1, J3                                                             | SMA Connector      | IN+             |  |

| J2                                                                 | SIP3               | Out             |  |

| J4, J5                                                             | Test Point         | Test Point      |  |

| R <sub>1</sub> , R <sub>2</sub> , R <sub>3</sub> , R <sub>4</sub>  | 0805 Capacitor     | 549             |  |

| R <sub>5</sub> , R <sub>8</sub>                                    | 0805 Capacitor     | 1.24k           |  |

| R <sub>6</sub> , R <sub>7</sub> , R <sub>9</sub> , R <sub>10</sub> | 0805 Capacitor     | 14.3k           |  |

| R <sub>11</sub> , R <sub>12</sub>                                  | 0805 Capacitor     | 22              |  |

| R <sub>13</sub> , R <sub>14</sub>                                  | 0805 Capacitor     | 50              |  |

| U1                                                                 | 8-Pin SOIC         | LMH6612/LMH6619 |  |

5

### **Measurement Hints**

It is important to connect the input source ground with the supply ground. For each ADC driver configuration, it is important to account for the impedance of the signal source when setting up the resistor networks to ensure that the differential outputs have the same gain. For example, an audio precision signal generator has about  $22\Omega$  of source impedance and the typical board termination is  $50\Omega$ , so the gain and input signal must be adjusted in order to obtain the desired signal at the output of the op amp.

# **Layout Considerations**

The following are recommendations for PCB layout in order to obtain the optimum high frequency performance:

- Place the ADC and amplifier as close together as possible.

- Put the supply bypassing capacitors as close as possible to the device (<1").</li>

- Utilize surface mount components instead of through-hole components.

- Keep the traces short where possible.

- Use terminated transmission lines for long traces.

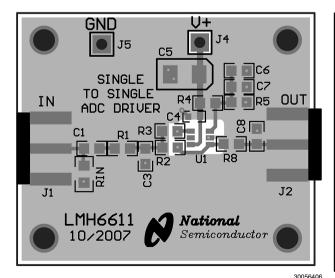

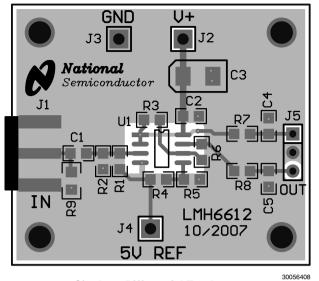

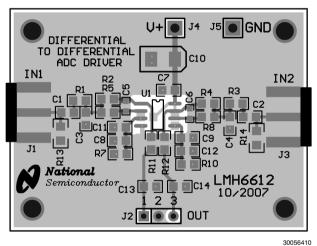

The top and bottom layouts of all three ADC driver configurations are shown in Figure 4 below.

Single to Single Top Layer

Single to Single Bottom Layer

30056407

SINGLE-ENDED

TO DIFFERENTIAL

ADC DRIVER

Single to Differential Top Layer

Single to Differential Bottom Layer

30056409

**Differential to Differential Bottom Layer**

30056411

FIGURE 4. Top and Bottom Layouts of All Three ADC Driver Configurations

AN-1812

### **Notes**

For more National Semiconductor product information and proven design tools, visit the following Web sites at:

| Products                       |                              | Design Support          |                                |

|--------------------------------|------------------------------|-------------------------|--------------------------------|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH                 | www.national.com/webench       |

| Audio                          | www.national.com/audio       | Analog University       | www.national.com/AU            |

| Clock Conditioners             | www.national.com/timing      | App Notes               | www.national.com/appnotes      |

| Data Converters                | www.national.com/adc         | Distributors            | www.national.com/contacts      |

| Displays                       | www.national.com/displays    | Green Compliance        | www.national.com/quality/green |

| Ethernet                       | www.national.com/ethernet    | Packaging               | www.national.com/packaging     |

| Interface                      | www.national.com/interface   | Quality and Reliability | www.national.com/quality       |

| LVDS                           | www.national.com/lvds        | Reference Designs       | www.national.com/refdesigns    |

| Power Management               | www.national.com/power       | Feedback                | www.national.com/feedback      |

| Switching Regulators           | www.national.com/switchers   |                         |                                |

| LDOs                           | www.national.com/ldo         |                         |                                |

| LED Lighting                   | www.national.com/led         |                         |                                |

| PowerWise                      | www.national.com/powerwise   |                         |                                |

| Serial Digital Interface (SDI) | www.national.com/sdi         |                         |                                |

| Temperature Sensors            | www.national.com/tempsensors |                         |                                |

| Wireless (PLL/VCO)             | www.national.com/wireless    |                         |                                |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLÉTENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS. NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2008 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email:

National Semiconductor Europe **Technical Support Center** Email: europe.support@nsc.com German Tel: +49 (0) 180 5010 771 English Tel: +44 (0) 870 850 4288

National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com

National Semiconductor Japan Email: jpn.feedback@nsc.com