# **Common Data** Transmission Parameters and their Definitions

### Overview

The scope of this application note is to introduce common data transmission parameters and to provide their definitions. This application note is subdivided into five sections, which are:

- Voltage Parameters

- **Current Parameters**

- **Timing Parameters**

- Miscellaneous Parameters

- Truth Table Explanations

Each parameter definition typically includes the following information: symbol, full name, description of measurement, measurement diagram, and a list of alternate names where applicable. Due to historical reasons (Fairchild origin, National origin, second sourcing, etc.) some devices use alternate symbols for the same parameters. Whenever possible, a list of common alternate symbols is provided for cross reference. New and future devices from National's Data Transmission Products Group will use the parameters as described in this application note for consistency and clarity reasons and to limit confusion.

This application note will be revised to add new parameters as required by new product definition.

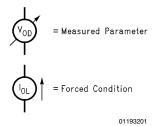

In this application note the following symbols are used in test circuit diagrams. The measured parameter symbol represents a PMU-Precision Measurement Unit located at the test points illustrated in the test circuit. The PMU symbol also includes the parameter's name that is under test. The forced condition represents a forced voltage or current which is required to make the parameter measurement. Once again, it includes the parameter symbol that is being forced.

# **Voltage Parameters**

### **INPUT VOLTAGE PARAMETERS**

V<sub>CI</sub> — Input Clamp Voltage. An input voltage in a region of relatively low differential resistance that serves to limit the input voltage swing.

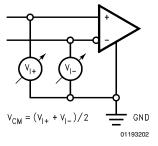

V<sub>CM</sub>—Common Mode Voltage. The algebraic mean of the two voltages applied to the referenced terminals, for example the receiver's input terminals. This voltage is referenced to circuit common (ground). This parameter is illustrated in Figure 1 along with its mathematical equation.

National Semiconductor Application Note 912 John Goldie October 1993

FIGURE 1. Common Mode Voltage

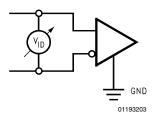

V<sub>DIFF</sub> — Differential Input Voltage. The potential difference between the input terminals of the device (receiver) with respect to one of the inputs (typically the inverting input terminal). This parameter may be a positive or negative voltage, and commonly specifies the minimum operating voltage and the absolute maximum differential input voltage. See Figure 2. V<sub>DIFF</sub> is also known as V<sub>ID</sub> for input differential voltage.

FIGURE 2. Differential Input Voltage

VIH - High-Level Input Voltage. An input voltage within the more positive (less negative) of the two ranges of values used to represent the binary variables. For example an input voltage between 2.0V and 5.0V in the case of standard TTL logic.

Note: A minimum is specified that is the least positive value of the high-level input voltage for which operation of the logic element within specification limits is quaranteed.

V<sub>IL</sub>—Low-Level Input Voltage. An input voltage within the less positive (more negative) of the two ranges of values used to represent the binary variables. For example an input voltage between 0.0V and 0.8V in the case of standard TTL logic.

Note: A maximum is specified that is the most positive value of the low-level input voltage for which operation of the logic element within specification limits is guaranteed.

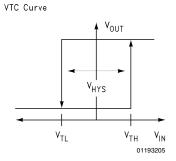

V<sub>TH</sub>-Positive-Going Threshold Voltage. The voltage level at a transition-operated input that causes operation of the logic element according to specification, as the input voltage rises from a level below the negative-going threshold voltage,  $V_{TL}$ . See Figure 3. Note that  $V_{TH}$  has also been

# Voltage Parameters (Continued)

used in the past to specifiy both thresholds in one parameter. In this case,  $V_{TH}$  represents the Threshold Voltages and supports a minimum and maximum limit, for example,  $\pm 200$  mV.

Voltage Transfer Curve (VTC)

VOH

VOH

VTH VIN

01193204

FIGURE 3. Threshold Voltages

$V_{TL}$ —Negative-Going Threshold Voltage. The voltage level at a transition-operated input that causes operation of the logic element according to specification, as the input voltage falls from a level above the positive-going threshold voltage,  $V_{TH}$ . See *Figure 3* above.

$V_{HYS}$ —Hysteresis. The absolute difference in voltage value between the positive going threshold and the negative going threshold. See *Figure 4*. Hysteresis is the most widely symbolized parameter. Alternate symbols include:  $V_{HY}$ ,  $V_{T+}-V_{T-}$ ,  $V_{HYST}$ ,  $\Delta V_{TH}$ ,  $V_{TH}-V_{TL}$ , and  $V_{HST}$ .

FIGURE 4. Hysteresis Voltage

# **Output Voltage Parameters**

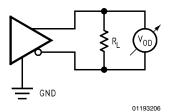

$V_{OD}$ —Output Differential Voltage. The output voltage between the output terminals of a differential driver with input conditions applied that, according to the product specification, will establish a voltage level at the output. This voltage is measured with respect to the inverting output of the differential driver.  $V_{OD}$  is defined as the voltage at true output (A,  $D_{OUT}$ +, or DO) minus the voltage at the inverting output (B,  $D_{OUT}$ -, or DO\*). Commonly an alpha-numeric suffix is added to designate specific test conditions. For example the case of different resistive loads. Also a star "\*" or over-score bar is used with the parameter to designate the parameters'

value with the opposite input state applied. This parameter has also been designated Terminated Output Voltage  $(V_T)$  in some datasheets.

FIGURE 5. V<sub>OD</sub> Test Circuit

$\Delta \textbf{V}_{\text{OD}}$ — Output Voltage Unbalance. The change in magnitude of the differential output voltage between the output terminals of a differential driver with opposite input conditions applied.  $\Delta \textbf{V}_{\text{OD}}$  is defined as:  $\Delta \textbf{V}_{\text{OD}} = |\textbf{V}_{\text{OD}}| - |\textbf{V}_{\text{OD}}^*|$ .

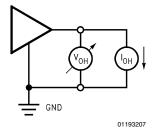

V<sub>OH</sub>—High Level Output Voltage. The output voltage at an output terminal with input conditions applied that, according to the product specification, will establish a logic high level at the output. This voltage is measured with respect to circuit common (ground). See *Figure 6*.

FIGURE 6. V<sub>OH</sub> Test Circuit

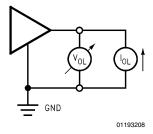

**V<sub>OL</sub>—Low Level Output Voltage.** The output voltage at an output terminal with input conditions applied that, according to the product specification, will establish a logic low level at the output. This voltage is measured with respect to circuit common (ground). See *Figure 7*.

FIGURE 7. V<sub>OL</sub> Test Circuit

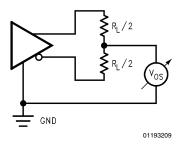

V<sub>os</sub>—Offset Voltage. The center point output voltage between the output terminals of a differential driver with input conditions applied that, according to the product specification, will establish a voltage level at the output. This voltage

www.national.com

# **Output Voltage Parameters**

(Continued)

is measured with respect to the driver's circuit common (ground). Commonly a star "\*" or over-score bar is used with the parameter to designate the parameter's value with the opposite input state applied (see *Figure 8*). This parameter is also referred to as  $V_{\rm OC}$ —Common Mode Voltage.

FIGURE 8. Vos Test Circuit

$\Delta V_{OS}$ —Offset Voltage Unbalance. The change in magnitude of the offset voltage at the output terminals of a differential driver with opposite input conditions applied.  $\Delta V_{OS}$  is defined as:

$$\Delta V_{OS} = |V_{OS}| - |V_{OS}^*|$$

.

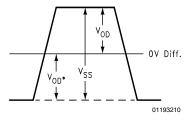

$m V_{SS}$ —Steady State Output Voltage. The steady state differential output voltage is defined as  $\rm |V_{OD}|$ + $\rm |V_{OD}$ \*I. This is typically a calculated parameter only, based on the formula shown above. The  $\rm V_{OD}$  parameter is defined above and illustrated in *Figure 5*.  $\rm V_{SS}$  is equal to twice the magnitude of  $\rm V_{OD}$  and is shown in *Figure 9*.

FIGURE 9. Differential Output Steady State Voltage

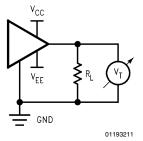

V<sub>T</sub>—Terminated Output Voltage. The output voltage at an output terminal with input conditions applied that, according to the product specification, will establish a known logic level at the output. This voltage is measured with respect to circuit common (ground) with a stated resistance, and may be a positive or negative voltage. This parameter is typically used in conjunction with single-ended (unbalanced) line drivers. See *Figure 10*.

FIGURE 10. V<sub>T</sub> Test Circuit

$$\Delta V_T = |V_T| - |V_T^*|$$

.

### **Current Parameters**

Note: Current is specified as magnitude value only, with the sign denoting the current direction only. A negative sign defines current flowing out of a device pin, while a positive sign defines current flowing into a device pin. The largest current limit is specified as a maximum, and zero (0) by default is the smallest minimum. All future DTP datasheets will follow this convention, and only some existing datasheets follow this convention.

**I**<sub>IH</sub>—**High-Level Input Current.** The current into (out of) an input when a high-level voltage is applied to that input. Note that current out of a device pin is given as a negative value. Typically this parameter specifies a positive maximum value for bipolar devices.

$I_{\rm IL}$ —Low-Level Input Current. The current into (out of) an input when a low-level voltage is applied to that input. Note that current out of a device pin is given as a negative value.

**I<sub>I</sub>—Maximum Input Current.** The current into (out of) an input when the maximum specified input voltage is applied to that input. Note that current out of a device pin is given as a negative value.

$I_{\rm IN}$ —Input Current. The current into (out of) a receiver input when a specified input voltage, or voltage range is applied to that input. Note that current out of a device pin is given as a negative value. This parameter is typically tested at the maximum voltage specified for the input. For differential receivers the other input (not under test) is held at 0V (in the case of RS-422/3 and 485 receivers).

I<sub>ING</sub>—Input Current, Power Up Glitch. The current into (out of) an input when a specified input voltage, or voltage range is applied to that input. Note that current out of a device pin is given as a negative value. This parameter applies to transceivers (RS-485) only, and is actually specifying the driver's performance at a specific power supply

3 www.national.com

### **Current Parameters** (Continued)

level. Additionally the driver is biased such that it is enabled, with the specified power supply voltage applied. This parameter assures that the driver is disabled by an internal circuit at the specified power supply level, even though the enable pin is active. If the driver was enabled,  $I_{\rm OS}$  current would be observed, instead of the combined measured current of driver TRI-STATE® leakage ( $I_{\rm OZ}$ ) plus receiver input current ( $I_{\rm IN}$ ). For example  $V_{\rm CC}{=}3.0{\rm V}$  is commonly referenced to represent a single point in a power up/down cycle. (See AN-905 for more information on this parameter).

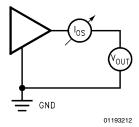

$I_{\rm OS}$ —Output Short Circuit Current. The current into (out of) an output when that output is short-circuited to circuit common (ground) or any other specified potential, with input conditions as noted, typically such that the output logic level is the furthest potential from the applied voltage. This parameter commonly includes an identifying suffix. For example  $I_{\rm OSD}$  represents the output short circuit current of a driver, while  $I_{\rm OSR}$  represents the receiver's output short circuit current. Output short circuit current is also designated by the following symbols:  $I_{\rm O+}$ ,  $I_{\rm SC}$ , and  $I_{\rm S}$ . See Figure 11.

FIGURE 11. I<sub>OS</sub> Test Circuit

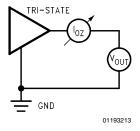

$I_{OZ}$ —TRI-STATE Output Current. The current into (out of) a TRI-STATE output having input (control) conditions applied that, according to the product specification, will establish a high impedance state at the output. This parameter commonly includes an identifying suffix. For example,  $I_{OZD}$  represents the TRI-STATE output current of a driver, while  $I_{OZR}$  represents the receiver's TRI-STATE output current. In addition  $I_{OZH}$  and  $I_{OZL}$  are also commonly used and denote the forced voltage (logic) level. See *Figure 12*.

FIGURE 12. Ioz Test Circuit

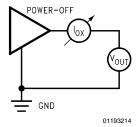

I<sub>OX</sub> — Power Off Leakage Current. The current flowing into (out of) an output with input conditions applied that, according to the product specification, will establish a high impedance state at the output. Commonly a known state is required on the power supply pin as an input condition. For example, power supply terminal ( $V_{\rm CC}$ ) equal to zero volts may be a required condition of an  $I_{\rm OX}$  parameter. See *Figure 13*.

FIGURE 13. I<sub>OX</sub> Test Circuit

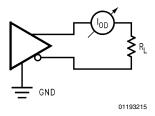

**I<sub>OD</sub>**—**Differential Output Current.** The current flowing between the output terminals of a differential line driver with an external differential load applied that, according to the product specification, will establish a known state at the output. See *Figure 14*.

FIGURE 14. Differential Output Current

**I<sub>OH</sub>**—**High-Level Output Current.** The current into (out of) an output terminal with input conditions applied that, according to the product specification, will establish a logic high level at the corresponding output. Note that current out of a terminal is given as a negative value.

**I<sub>OL</sub>—Low-Level Output Current.** The current into (out of) an output terminal with input conditions applied that, according to the product specification, will establish a logic low level at the corresponding output. Note that current out of a terminal is given as a negative value.

$I_{\rm CC}$ —Supply Current. The current into the  $V_{\rm CC}$  supply terminal of the integrated circuit. Normally the parameter is measured with all loads removed. It may also include a suffix that denotes that state of the device. For example:

I<sub>CCD</sub>= Power Supply Current (drivers enabled, receivers disabled)

I<sub>CCR</sub>= Power Supply Current (receivers enabled, drivers disabled)

I<sub>CCZ</sub>= Power Supply Current (drivers and receivers disabled)

I<sub>CCX</sub>= Power Supply Current (sleep or shutdown mode)

**I<sub>EE</sub>—Supply Current.** The current into the V<sub>EE</sub> supply terminal of the integrated circuit. Normally the parameter is measured with all loads removed. It may also include a suffix that denotes that state of the device. Note that current out of

### Current Parameters (Continued)

a terminal is given as a negative value. For example:

I<sub>EED</sub>= Power Supply Current

(drivers enabled, receivers disabled)

I<sub>EER</sub>= Power Supply Current

(receivers enabled, drivers disabled)

I<sub>EEZ</sub>= Power Supply Current

(drivers and receivers disabled)

I<sub>EEX</sub>= Power Supply Current (sleep or shutdown mode)

## **Timing Parameters**

t<sub>PLH</sub>—Propagation Delay Time, Low-to-High-Level Output. The time between specified reference points on the input and output voltage waveforms with the output changing from a logic low level to a logic high level.

t<sub>PHL</sub>—Propagation Delay Time, High-to-Low-Level Output. The time between specified reference points on the input and output voltage waveforms with the output changing from a logic high level to a logic low level.

$t_{\rm SK}$ —Propagation Delay Skew. The magnitude difference between complementary propagation delays. Skew is defined as  $|t_{\rm PLH}-t_{\rm PHL}|$ . This specification is a per channel parameter unless specified otherwise.

t<sub>PLHD</sub>—Differential Propagation Delay Time, Low-to-High-Level Output. The time between specified reference points on the input and output differential voltage waveforms with the output changing from a logic low level to a logic high level.

t<sub>PHLD</sub>—Differential Propagation Delay Time, High-to-Low-Level Output. The time between specified reference points on the input and output differential voltage waveforms with the output changing from a logic high level to a logic low level.

${f t_{SKD}}$ —Differential Propagation Delay Skew. The magnitude difference between complementary differential propagation delays. Skew is defined as  ${f l_{PLHD}}$ - ${f l_{PHLD}}{f l}$ . This specification is a per channel parameter unless specified otherwise.

${f t_{PZH}}$ —Output Enable Time. The propagation delay time between the specified reference points on the input (control) and output voltage waveforms with the TRI-STATE output changing from a high impedance (off) state to a logic high lovel.

${f t_{PZL}}$ —Output Enable Time. The propagation delay time between the specified reference points on the input (control) and output voltage waveforms with the TRI-STATE output changing from a high impedance (off) state to a logic low level.

${f t_{PHZ}}$ —Output Disable Time. The propagation delay time between the specified reference points on the input (control) and output voltage waveforms with the TRI-STATE output changing from logic high level to a high impedance (off) state

**t<sub>PLZ</sub>—Output Disable Time.** The propagation delay time between the specified reference points on the input (control) and output voltage waveforms with the TRI-STATE output changing from logic low level to a high impedance (off) state.

${\it t_{PSH}-Propagation}$  Delay Time, Sleep-to-High-Level Output. The propagation delay time between the specified

reference points on the input (control) and output voltage waveforms with the output changing from an off state to a logic high level.

**t<sub>PSL</sub>** — **Propagation Delay Time, Sleep-to-Low-Level Output.** The propagation delay time between the specified reference points on the input (control) and output voltage waveforms with the output changing from an off state to a logic low level.

t<sub>PHS</sub>—Propagation Delay Time, High-Level Output to Sleep. The propagation delay time between the specified reference points on the input (control) and output voltage waveforms with the output changing from logic high level to an off state.

**t<sub>PLS</sub>**—**Propagation Delay Time, Low-Level Output to Sleep.** The propagation delay time between the specified reference points on the input (control) and output voltage waveforms with the output changing from logic low level to an off state.

$t_r$ —Rise Time. The time between two specified reference points on an input waveform, normally between the 10% and 90% or the 20% and 80% points, that is changing from low to high. Note, also commonly specified as transition time ( $t_{TLH}$ ).

${\bf t_f}$ —Fall Time. The time between two specified reference points on an input waveform, normally between the 10% and 90% or the 20% and 80% points, that is changing from high to low. Note, also commonly specified as transition time ( $t_{THL}$ ).

${

m t_{TLH}}$ —Transition Time Low to High. The time between two specified reference points on an input waveform, normally between the 10% and 90% or the 20% and 80% points, that is changing from low to high. Note, also commonly specified as rise time ( ${

m t_r}$ ).

${\bf t_{THL}}$ —Transition Time High to Low. The time between two specified reference points on an output waveform, normally between the 10% and 90% or the 20% and 80% points, that is changing from high to low. Note, also commonly specified as fall time ( ${\bf t_f}$ ).

${\bf t_{NW}}$ —Noise Pulse Width. The width in time of a pulse applied to a device. The parameter is commonly specified with receivers that feature low pass noise filters.  ${\bf t_{NW}}$  is the pulse width assumed to be noise and guaranteed to be rejected.

### Miscellaneous Parameters

**SR**—**Slew Rate.** The time between two specified reference points on an output waveform, normally between the  $\pm 3V$  level for TIA/EIA-232 (RS-232) drivers, divided by the voltage difference. Note, this parameter is normally specified in Volts per microsecond (V/ $\mu$ s). A suffix may be added to denote different loading conditions.

$R_{IN}$ —Input Resistance. The slope of the input voltage vs. input current curve of an input when a specified voltage range is applied to that input and the current is measured. Note, that two points must be measured for the parameter to be calculated correctly as  $R_{IN}$  is defined as  $\Delta V/\Delta I$  not V/I.

**R<sub>OUT</sub>—Output Impedance.** The resulting output impedance calculated from measured currents at applied voltages.

# **Truth Table Explanantions**

Symbols generally associated with functional truth tables are listed below:

H or 1 = Logic High Level (steady state)

# **AN-912**

# Truth Table Explanantions (Continued)

L or 0 = Logic Low Level (steady state)

Z = TRI-STATE® (high impedance off state) X = irrelevant (input, including transitions)

### References

ALS/AS IC Device Testing, ALS/AS Logic Databook. National Semiconductor Corp., 1990

Glossary of Terms, ALS/AS Logic Databook. National Semiconductor Corp., 1990

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Email: support@nsc.com

www.national.com

**National Semiconductor** Europe

Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +44 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790

**National Semiconductor** Asia Pacific Customer Response Group Tel: 65-2544466 Fax: 65-2504466 Email: ap.support@nsc.com **National Semiconductor** Tel: 81-3-5639-7560 Fax: 81-3-5639-7507