# AN-929

# Microcontroller Interface to the ADC12038 Families

National Semiconductor Application Note 929 Emmy Denton February 1994

## **Table of Contents**

| 1.0 General Overview                                               |

|--------------------------------------------------------------------|

| 1.1 THE SERIAL INTERFACE                                           |

| 1.2 THE SERIAL OUTPUT WORD FORMAT                                  |

| 1.3 SELECTING OUTPUT WORD FORMAT AND MODE                          |

| 1.4 MULTIPLEXER ADDRESSING                                         |

| 1.5 STATUS REGISTER DEFINITION                                     |

| 1.6 PROGRAMMING PROCEDURE                                          |

| 2.0 General Flow Chart for a Microcontroller Interface             |

| 3.0 Examples of Microcontroller Hardware Implementations           |

| 3.1 THE 68HC11                                                     |

| 3.2 NATIONAL'S HPC AND COP 11                                      |

| 3.3 THE 8051 1 <sup>-</sup>                                        |

| 4.0 68HC11 SPI Interface                                           |

| 4.1 68HC11 SPI PORT AND REGISTER INITIALIZATION FOR THE ADC12038 1 |

| 4.1.1 DDRD                                                         |

| 4.1.2 SPCR                                                         |

| 4.2 68HC11 Program Listing                                         |

| 5.0 Beferences                                                     |

COPS™, HPC™ and MICROWIRE™ are trademarks of National Semiconductor Corporation.

#### 1.0 General Overview

The ADC12038 families are 12-bit plus sign sampling ADC converters with serial I/O. These devices have configurable analog multiplexers with 2, 4, or 8 input channels. On request, these A/Ds perform a self calibration routine that minimizes linearity, zero, and full-scale errors. To minimize power consumption these devices have a power down mode that can be accessed by hardware (PD pin) or by a software instruction.

The serial I/O is configured to comply with the NSC MICROWIRE™ serial data exchange standard for easy interface to the COPS™ and HPC families of controllers, and can easily interface with standard shift registers and microprocessors. The conversion resolution can be selected by a

software instruction to be 8-bits, 8-bits+sign, 12-bits or 12-bits+sign. 8-bit and 8-bit+sign conversions take less time than 12-bit and 12-bit+sign conversions (21 clock periods versus 44). In addition, selection of the output data format can be software programmable to be:

- 1. 8-bits, 8-bits+sign, 12-bits, 12-bits+sign, 16-bits or 16-bits+sign in length

- 2. MSB or LSB first

- 3. Left or Right justified

There are three ADC12038 families: Low voltage, High speed and standard. Each family includes four different combinations of analog inputs and features as summarized in *Table 1*.

TABLE 1. Summary of the Differences of the Devices in the Three ADC12038 Families

|           | Operating    | Maximum   |            |        | MUX OUT | Hardware |                 |

|-----------|--------------|-----------|------------|--------|---------|----------|-----------------|

| Device    | Supply       | Clock     | Maximum    | Number | and     | Power    | Package Size    |

| Number    | Voltage      | Frequency | Sampling   | of MUX | A/D IN  | Down     | and Type        |

|           | and Power    | (MHz)     | Rate (kHz) | Inputs | Pins    | Control  |                 |

|           | Dissipation  |           |            |        |         | (PD Pin) |                 |

| ADC12030  | 5V ±10% 33   | 5 MHz     | 73 kHz     | 2      | NO      | NO       | 16-pin DIP & SO |

| ADC12032  | mW (max) @5V |           |            | 2      | YES     | NO       | 20-pin DIP & SO |

| ADC12034  |              |           |            | 4      | YES     | YES      | 24-pin DIP & SO |

| ADC12038  |              |           |            | 8      | YES     | YES      | 28-pin DIP & SO |

| ADC12L030 | 3.3V ±10%    |           |            | 2      | NO      | NO       | 16-pin DIP & SO |

| ADC12L032 | 15 mW (max)  |           |            | 2      | YES     | NO       | 20-pin DIP & SO |

| ADC12L034 | @3.3V        |           |            | 4      | YES     | YES      | 24-pin DIP & SO |

| ADC12L038 |              |           |            | 8      | YES     | YES      | 28-pin DIP & SO |

| ADC12H030 | 5V ±10% 36   | 8 MHz     | 116 kHz    | 2      | NO      | NO       | 16-pin DIP & SO |

| ADC12H032 | mW (max) @5V |           |            | 2      | YES     | NO       | 20-pin DIP & SO |

| ADC12H034 |              |           |            | 4      | YES     | YES      | 24-pin DIP & SO |

| ADC12H038 |              |           |            | 8      | YES     | YES      | 28-pin DIP & SO |

Throughout this application note we will refer to the ADC12038. Any of this information will also apply to all the devices in the ADC12038 families. The device data sheets should be used in conjunction with this application note to help you understand the operation of these devices. The scope of this application note will focus on the digital interface. A brief overview of the digital functionality of these devices is included.

#### 1.1 THE SERIAL INTERFACE

The ADC12038 families of analog-to-digital converters can be programmed for many modes of operation through their serial digital interface. The serial interface for the ADC12038 is comprised of the digital control lines SCLK,  $\overline{CS}$ , DO, DI, EOC,  $\overline{DOR}$ , PD and  $\overline{CONV}$ . Table 2 gives a brief pin description for each of these control lines.

#### **TABLE 2. Digital Control Pin Descriptions**

| Pin<br>Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCLK        | This is the serial data clock input. The clock applied to this input controls the rate at which the serial data exchange occurs. With $\overline{CS}$ low the rising edge of SCLK loads the information on the DI pin into the multiplexer address and mode select shift register. This address controls which channel of the analog input multiplexer (MUX) is selected and the mode of operation for the ADC. With $\overline{CS}$ low the falling edge shifts of SCLK the data resulting from the previous ADC conversion out on DO, with the exception of the first bit of data. When $\overline{CS}$ is low continuously, the first bit of the data is clocked out on the rising edge of EOC (end of conversion). When $\overline{CS}$ is toggled the falling edge of $\overline{CS}$ always clocks out the first bit of data. $\overline{CS}$ should be brought low when SCLK is low. |

| CS          | This is the chip select pin. When a logic low is applied to this pin the device is selected, activating the DO, DI, and SCLK serial interface lines. The falling edge of $\overline{CS}$ resets a conversion in progress and starts the sequence for a new conversion. When $\overline{CS}$ is brought low during a conversion in progress, the conversion is prematurely ended and the data in the output latches may be corrupted, requiring the data output at this time to be ignored. $\overline{CS}$ should be brought low when SCLK is low.                                                                                                                                                                                                                                                                                                                                          |

| DI          | The data input pin. The data applied to this pin is shifted by the rising edge of SCLK into the multiplexer address and mode select register. <i>Tables 4, 5, 6, 7</i> show the assignments of the multiplexer address and the mode select data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DO          | The data output pin. This pin is an active push/pull output when $\overline{CS}$ is Low. When $\overline{CS}$ is High this output is in TRI-STATE. The ADC conversion result and converter status data are clocked out by the falling edge of SCLK on this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| EOC         | This pin is an active push/pull output and indicates the status of the device. When Low, it signals that the ADC is busy with a conversion, auto-calibration, auto-zero or power down cycle. The rising edge of EOC signals the end of one of these cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DOR         | This is the data output ready pin. This pin is an active push/pull output. It is useful only when $\overline{CS}$ is toggled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CONV        | A logic Low is required on this pin to program any mode or change the ADC's configuration (12-bit conversion, 8-bit conversion, Auto Cal, Auto Zero etc.) as listed in the Mode Programming Table ( <i>Table 4</i> ). When this pin is high the ADC is placed in the read data only mode. While in the read data only mode, bringing $\overline{CS}$ low and Pulsing SCLK will only clock out on DO any data stored in the ADCs output shift register. The data on DI will be neglected. A new conversion will not be started and the ADC will remain in the mode and/or configuration previously programmed. Read data only cannot be performed while a conversion, Auto-Cal or Auto-Zero are in progress.                                                                                                                                                                                 |

| PD          | This is the power down pin. When PD is high, the ADC is powered down; when PD is low, the ADC is powered up.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

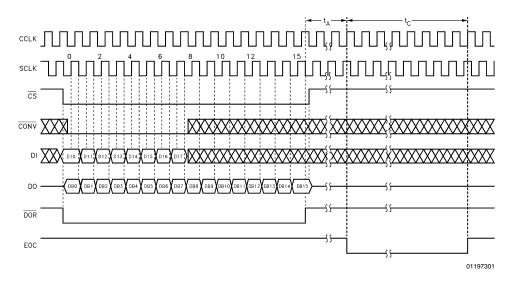

The interplay of these lines can be graphically seen in the timing diagram of *Figure 1*.

The chip select pin  $(\overline{CS})$  enables the logic inputs and DO output. Eight bits of data that control the ADC are clocked in on the digital input pin (DI) by the rising edge of the serial clock (SCLK) when  $\overline{CS}$  is low. Taking  $\overline{CS}$  will output the first bit of data (DBO) on DO. While  $\overline{CS}$  is low, the falling edge of SCLK clocks the data out on the digital output pin (DO).  $\overline{CS}$  should only be brought low when SCLK is low. The functions of the convert input  $(\overline{CONV})$ , data output ready  $(\overline{DOR})$  and end of conversion output (EOC) pins are covered in more detail in the data sheet. The simplest interface to the

ADC12038 requires only 4 control lines: DO, DI, SCLK and CS. For this case CONV and PD are grounded and EOC and DOR outputs are not used.

#### 1.2 THE SERIAL OUTPUT WORD FORMAT

The diagram in *Figure 2* shows a 16-bit serial output word. The ADC12038 family can be programmed to provide unsigned output data in 8-bit, 12-bit, or 16-bit word lengths or signed data in 9-bit, 13-bit, or 17-bit word lengths. The data format can be right- or left-justified, MSB or LSB first. *Table 3* summarizes the available serial output data formats. *Table 4* describes the serial input word required to select the available serial output data formats.

FIGURE 1. Timing Diagram for a 12-Bit Plus Sign Conversion with a 16-Bit Serial Output Word Format on DO

**TABLE 3. Data Out Formats**

| DO      | Forma | ts   | DB0  | DB1  | DB2  | DB3  | DB4  | DB5 | DB6 | DB7 | DB8  | DB9 | DB10 | DB11 | DB12 | DB13 | DB14 | DB15 | DB16 |

|---------|-------|------|------|------|------|------|------|-----|-----|-----|------|-----|------|------|------|------|------|------|------|

| with    | MSB   | 17   | Sign | Sign | Sign | Sign | Sign | MSB | 10  | 9   | 8    | 7   | 6    | 5    | 4    | 3    | 2    | 1    | LSB  |

| Sign    | First | Bits |      |      |      |      |      |     |     |     |      |     |      |      |      |      |      |      |      |

|         |       | 13   | Sign | MSB  | 10   | 9    | 8    | 7   | 6   | 5   | 4    | 3   | 2    | 1    | LSB  |      |      |      |      |

|         |       | Bits |      |      |      |      |      |     |     |     |      |     |      |      |      |      |      |      |      |

|         |       | 9    | Sign | MSB  | 6    | 5    | 4    | 3   | 2   | 1   | LSB  |     |      |      |      |      |      |      |      |

|         |       | Bits |      |      |      |      |      |     |     |     |      |     |      |      |      |      |      |      |      |

|         | LSB   | 17   | LSB  | 1    | 2    | 3    | 4    | 5   | 6   | 7   | 8    | 9   | 10   | MSB  | Sign | Sign | Sign | Sign | Sign |

|         | First | Bits |      |      |      |      |      |     |     |     |      |     |      |      |      |      |      |      |      |

|         |       | 13   | LSB  | 1    | 2    | 3    | 4    | 5   | 6   | 7   | 8    | 9   | 10   | MSB  | Sign |      |      |      |      |

|         |       | Bits |      |      |      |      |      |     |     |     |      |     |      |      |      |      |      |      |      |

|         |       | 9    | LSB  | 1    | 2    | 3    | 4    | 5   | 6   | MSB | Sign |     |      |      |      |      |      |      |      |

|         |       | Bits |      |      |      |      |      |     |     |     |      |     |      |      |      |      |      |      |      |

| without | MSB   | 16   | 0    | 0    | 0    | 0    | MSB  | 10  | 9   | 8   | 7    | 6   | 5    | 4    | 3    | 2    | 1    | LSB  |      |

| Sign    | First | Bits |      |      |      |      |      |     |     |     |      |     |      |      |      |      |      |      |      |

|         |       | 12   | MSB  | 10   | 9    | 8    | 7    | 6   | 5   | 4   | 3    | 2   | 1    | LSB  |      |      |      |      |      |

|         |       | Bits |      |      |      |      |      |     |     |     |      |     |      |      |      |      |      |      |      |

|         |       | 8    | MSB  | 6    | 5    | 4    | 3    | 2   | 1   | LSB |      |     |      |      |      |      |      |      |      |

|         |       | Bits |      |      |      |      |      |     |     |     |      |     |      |      |      |      |      |      |      |

|         | LSB   | 16   | LSB  | 1    | 2    | 3    | 4    | 5   | 6   | 7   | 8    | 9   | 10   | MSB  | 0    | 0    | 0    | 0    |      |

|         | First | Bits |      |      |      |      |      |     |     |     |      |     |      |      |      |      |      |      |      |

|         |       | 12   | LSB  | 1    | 2    | 3    | 4    | 5   | 6   | 7   | 8    | 9   | 10   | MSB  |      |      |      |      |      |

|         |       | Bits |      |      |      |      |      |     |     |     |      |     |      |      |      |      |      |      |      |

|         |       | 8    | LSB  | 1    | 2    | 3    | 4    | 5   | 6   | MSB |      |     |      |      |      |      |      |      |      |

|         |       | Bits |      |      |      |      |      |     |     |     |      |     |      |      |      |      |      |      |      |

The falling edge of SCLK strobes out the digital word on DO when  $\overline{CS}$  is low. The digital word length will vary in accord with the digital word format. Thus for 8-bits + sign resolution 9 clock cycles are required.

As shown in the timing diagram (*Figure 1*), the acquisition time (the period of time during which the analog input is being sampled) starts on the falling edge of the last data clock cycle. For 16 bits of data that would be the 16th clock; for 8 bits of data that would be the 8th clock. The length of the acquisition time may be programmed by the user with an instruction, (see *Table 4*). The acquisition time can be set to 6, 10, 18, or 34 CCLK cycles.

#### 1.3 SELECTING OUTPUT WORD FORMAT AND MODE

While  $\overline{\text{CS}}$  is low, the rising edge of SCLK strobes in the data bits DI0–DI7 on the DI control line. For the ADC12038, the values of DI0–DI7 determine the digital output word format, mode select, and multiplexer configuration. For the ADC12034, 7 bits of data (DI0–DI6) are required. The ADC12032, and ADC12030 require only 6 bits of data (DI0–DI5). Mode Select determines the number of clock periods for the acquisition time ( $t_A$ ), software power up/down, Auto Cal, Auto Zero and other functions as shown in *Table 4*.

#### **TABLE 4. Mode Programing**

| ADC12038       | DI0                                               | DI1    | DI2            | DI3         | DI4      | DI5 | DI6       | DI7               |                                   |                       |

|----------------|---------------------------------------------------|--------|----------------|-------------|----------|-----|-----------|-------------------|-----------------------------------|-----------------------|

| ADC12034       | DI0                                               | DI1    | DI2            |             | DI3      | DI4 | DI5       | DI6               |                                   | DO Format             |

| ADC12030       |                                                   |        |                |             |          |     |           |                   | Mode Select                       | (next Conversion      |

| and            | DI0                                               | DI1    |                |             | DI2      | DI3 | DI4       | DI5               | (Current)                         | Cycle)                |

| ADC12032       |                                                   |        |                |             |          |     |           |                   |                                   |                       |

|                | N                                                 | 1UX A  | Addres         | SS          | L        | L   | L         | L                 | 12-Bit Conversion                 | 12- or 13-Bit MSB Fir |

|                | see                                               | Table  | es 5,          | <i>6</i> or |          |     |           |                   |                                   |                       |

|                |                                                   | Tab    | ole 7          |             |          |     |           |                   |                                   |                       |

|                | N                                                 | 1UX A  | Addres         | ss          | L        | L   | L         | Н                 | 12-Bit Conversion                 | 16-Bit MSB First      |

|                | see                                               | Tabl   | es 5,          | <i>6</i> or |          |     |           |                   |                                   |                       |

|                |                                                   | Tab    | ole 7          |             |          |     |           |                   |                                   |                       |

| MUX Address    |                                                   |        | ss             | L           | L        | Н   | L         | 8-Bit Conversion  | 8- or 9-Bit MSB Firs              |                       |

|                | see                                               | Tabl   | es 5,          | <i>6</i> or |          |     |           |                   |                                   |                       |

|                |                                                   | Tab    | ole 7          |             |          |     |           |                   |                                   |                       |

|                | L                                                 | L      | L              | L           | L        | L   | Н         | Н                 | 12-Bit Conversion of Full-Scale   | 12- or 13-Bit MSB Fi  |

| MUX Addre      |                                                   | Addres | ss             | L           | Н        | L   | L         | 12-Bit Conversion | 12- or 13-Bit LSB Fir             |                       |

|                | see                                               |        | es 5,          | <i>6</i> or |          |     |           |                   |                                   |                       |

|                | Table 7                                           |        |                |             |          |     |           |                   |                                   |                       |

|                | MUX Address                                       |        |                |             | L        | Н   | L         | Н                 | 12-Bit Conversion                 | 16-Bit LSB First      |

|                | see <i>Tables 5, 6</i> or <i>Table 7</i>          |        |                | <i>6</i> or |          |     |           |                   |                                   |                       |

|                | <u> </u>                                          |        |                |             | <b>.</b> |     |           |                   | 0.5%                              | 0.000.100.5           |

|                |                                                   | -      | Addres         |             | L        | Н   | Н         | L                 | 8-Bit Conversion                  | 8- or 9-Bit LSB Firs  |

|                | see                                               |        | es 5,<br>ole 7 | <i>6</i> or |          |     |           |                   |                                   |                       |

|                | L                                                 | L      | L              | L           | L        | Н   | Н         | Н                 | 12-Bit Conversion of Offset       | 12- or 13-Bit LSB Fir |

|                |                                                   | L      | L              | L           | Н        | L   | L         | L                 | Auto Cal                          | No Change             |

|                |                                                   | -      |                | L           | Н.       | L   | L         | Н                 | Auto Zero                         | No Change             |

|                |                                                   | L      |                | L           | Н.       | L   | Н         | L                 | Power Up                          | No Change             |

|                |                                                   | L      | L              |             | Н.       | L   | Н.        | Н                 | Power Down                        | No Change             |

|                |                                                   | L      | L              | L           | Н        | Н   | L         | L                 | Read Status Register (LSB First)  | No Change             |

|                |                                                   | L      | L              | L           | Н        | H   | L         | Н                 | Data Out without Sign             | No Change             |

|                | H                                                 | L      | L              | L           | Н        | Н   | L         | Н                 | Data Out with Sign                | No Change             |

|                | <del>                                      </del> | L      | L              | L           | Н.       | Н   | Н         | L                 | Acquisition Time—4 CCLK Cycles    | No Change             |

|                | 1                                                 | Н      | L              | L           | H        | Н.  | Н.        | L                 | Acquisition Time—4 CCLK Cycles    | No Change             |

|                | H                                                 | L      | L              | L           | H        | H   | Н.        | L                 | Acquisition Time—16 CCLK Cycles   | No Change             |

|                | H                                                 | Н      | L              | L           | H        | H   | Н         | L                 | Acquisition Time — 32 CCLK Cycles | No Change             |

|                | <del>                                     </del>  |        | L              | L           | H        | H   | Н.        | Н                 | User Mode                         | No Change             |

| H L L L        |                                                   | -      | Н.             | Н.          | Н.       | Н.  | Test Mode | No Change         |                                   |                       |

| ''   -   -   - |                                                   |        |                | -           | ''       | ''  | ''        | ''                | (CH1–CH7 become Active Outputs)   | INO Offarige          |

Note: The A/D powers up with No CAL, No Auto-Zero, 10 CCLK Cycles Acquisition time, sign bit on, 13-bit MSB First format, power up, and user mode.

#### 1.4 MULTIPLEXER ADDRESSING

The analog input channel configuration is selected during mode programming using the "MUX address" bits in *Table 4*. These bits and their effects are defined in *Tables 5, 6, 7*.

TABLE 5. ADC12038 Multiplexer Addressing

|     | М   | JX   |     | Α   | nalog | Chan   | nel A  | ddres  | sed ar | nd Ass | signm | ent | A/D I | nput  | Multiplexer |         | Mode         |

|-----|-----|------|-----|-----|-------|--------|--------|--------|--------|--------|-------|-----|-------|-------|-------------|---------|--------------|

|     | Add | ress |     |     | ,     | with A | /D IN  | 1 tied | to MU  | IXOUT  | Γ1    |     | Pola  | arity | Output      | Channel |              |

|     |     |      |     |     |       | and A  | /D IN2 | 2 tied | to MU  | TUOX   | 2     |     | Assig | nment | Assig       | nment   |              |

| DI0 | DI1 | DI2  | DI3 | CH0 | CH1   | CH2    | СНЗ    | CH4    | CH5    | СН6    | CH7   | COM | A/D   | A/D   | MUXOUT1     | MUXOUT2 |              |

|     |     |      |     |     |       |        |        |        |        |        |       |     | IN1   | IN2   |             |         |              |

| L   | L   | L    | L   | +   | _     |        |        |        |        |        |       |     | +     | _     | CH0         | CH1     |              |

| L   | L   | L    | Н   |     |       | +      | _      |        |        |        |       |     | +     | _     | CH2         | CH3     |              |

| L   | L   | Н    | L   |     |       |        |        | +      | _      |        |       |     | +     | _     | CH4         | CH5     |              |

| L   | L   | Н    | Н   |     |       |        |        |        |        | +      | _     |     | +     | _     | CH6         | CH7     | Differential |

| L   | Н   | L    | L   | _   | +     |        |        |        |        |        |       |     | _     | +     | CH0         | CH1     |              |

| L   | Н   | L    | Н   |     |       | _      | +      |        |        |        |       |     | -     | +     | CH2         | CH3     |              |

| L   | Н   | Н    | L   |     |       |        |        | _      | +      |        |       |     | _     | +     | CH4         | CH5     |              |

| L   | Н   | Н    | Н   |     |       |        |        |        |        | _      | +     |     | -     | +     | CH6         | CH7     |              |

| Н   | L   | L    | L   | +   |       |        |        |        |        |        |       | _   | +     | _     | CH0         | COM     |              |

| Н   | L   | L    | Н   |     |       | +      |        |        |        |        |       | _   | +     | _     | CH2         | COM     |              |

| Н   | L   | Н    | L   |     |       |        |        | +      |        |        |       | _   | +     | _     | CH4         | COM     |              |

| Н   | L   | Н    | Н   |     |       |        |        |        |        | +      |       | _   | +     | _     | CH6         | COM     | Single-Ended |

| Н   | Н   | L    | L   |     | +     |        |        |        |        |        |       | _   | +     | _     | CH1         | COM     |              |

| Н   | Н   | L    | Н   |     |       |        | +      |        |        |        |       | _   | +     | _     | CH3         | COM     |              |

| Н   | Н   | Н    | L   |     |       |        |        |        | +      |        |       | _   | +     | _     | CH5         | COM     |              |

| Н   | Н   | Н    | Н   |     |       |        |        |        |        |        | +     | _   | +     | _     | CH7         | СОМ     |              |

#### TABLE 6. ADC12034 Multiplexer Addressing

| A   | MUX<br>Addres | s   | wit | and<br>h A/D IN | hannel A<br>Assignr<br>I1 tied to<br>2 tied to | ment<br>MUXOU | JT1 | Pola    | Input<br>arity<br>nment | Output  | Multiplexer Output Channel Assignment |              |  |

|-----|---------------|-----|-----|-----------------|------------------------------------------------|---------------|-----|---------|-------------------------|---------|---------------------------------------|--------------|--|

| DI0 | DI1           | DI2 | CH0 | CH1             | CH2                                            | СНЗ           | СОМ | A/D IN1 | A/D IN2                 | MUXOUT1 | MUXOUT2                               |              |  |

| L   | L             | L   | +   | -               |                                                |               |     | +       | -                       | CH0     | CH1                                   |              |  |

| L   | L             | Н   |     |                 | +                                              | _             |     | +       | _                       | CH2     | CH3                                   | Differential |  |

| L   | Н             | L   | _   | +               |                                                |               |     | _       | +                       | CH0     | CH1                                   |              |  |

| L   | Н             | Н   |     |                 | _                                              | +             |     | _       | +                       | CH2     | CH3                                   |              |  |

| Н   | L             | L   | +   |                 |                                                |               | _   | +       | -                       | CH0     | COM                                   |              |  |

| Н   | L             | Н   |     |                 | +                                              |               | _   | +       | _                       | CH2     | СОМ                                   | Single-      |  |

| Н   | Н             | L   |     | +               |                                                |               | _   | +       | _                       | CH1     | COM                                   | Ended        |  |

| Н_  | Н             | Н   |     |                 |                                                | +             | _   | +       | _                       | СНЗ     | COM                                   |              |  |

TABLE 7. ADC12032 and ADC12030 Multiplexer Addressing

|     | JX<br>ress | with A/I | g Channel Add<br>and Assignmen<br>O IN1 tied to MI<br>O IN2 tied to MI | it<br>UXOUT1 | Pola    | Input<br>arity<br>nment | Multij<br>Output<br>Assig | Mode |              |

|-----|------------|----------|------------------------------------------------------------------------|--------------|---------|-------------------------|---------------------------|------|--------------|

| DI0 | DI1        | CH0      | СОМ                                                                    | A/D IN1      | A/D IN2 | MUXOUT1                 | MUXOUT2                   |      |              |

| L   | L          | +        | _                                                                      |              | +       | -                       | CH0                       | CH1  | Differential |

| L   | Н          | _        | +                                                                      |              | _       | +                       | CH0                       | CH1  |              |

| Н   | L          | +        |                                                                        | -            | +       | _                       | CH0                       | COM  | Single-      |

| Н   | Н          |          | +                                                                      | _            | +       | _                       | CH1                       | СОМ  | Ended        |

Note: MUXOUT1, MUXOUT2, A/D IN1 and A/D IN2 pins are not available on the ADC12030. A/D IN1 is tied internally to MUXOUT1: A/D IN2 is tied internally to MUXOUT2

As can be seen in the tables, 4, 3 or 2 bits of the serial digital input word control the channel selection. These bits are part of an 8-, 7-, or 6-bit serial word that controls the function of the devices.

#### 1.5 STATUS REGISTER DEFINITION

On request, the ADC12038 provides status information indicating power up or power down status, output data format, Auto-Cal status, and User/Test Mode status. *Table 8* defines the digital output data obtained after requesting a "Status Read".

When  $\overline{CS}$  is used it is not necessary to clock all the status bits out.  $\overline{CS}$  may be brought high at any time to restart a new serial data communication.

#### 1.6 PROGRAMMING PROCEDURE

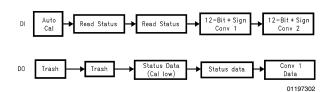

The example in *Figure 2* shows a typical sequence of events after power is applied to the ADC12038:

FIGURE 2. Typical Instruction Sequence after Power Up

The first instruction to the ADC via DI initiates Auto Cal. The data output on DO at that time is meaningless and is completely random. To obtain the specified accuracy of the device it is necessary to issue an Auto Cal instruction after the power supply and reference voltage to the device have been given enough time to stabilize. The Auto Cal instruction initiates an internal calibration sequence without which the specified accuracy of the device would be unattainable. To determine whether the Auto Cal has been completed, a Read Status instruction is issued to the device. Again, the data obtained while issuing the Read Status instruction has no significance since the Auto Cal instruction modifies the data in the output shift register. To retrieve the status information an additional read status instruction is issued to the ADC. At this time the status data is available on DO. If the Cal signal in the status word is low, Auto Cal has been completed. Therefore, the next instruction issued can start a conversion. The data output, while clocking in the "start conversion request", is again status information. Status can not be read during a conversion. To preserve the integrity of the A/D conversion, there is no end of conversion bit in the status word. If CS is brought low during a conversion, that conversion is stopped and never completed. EOC can be used to determine the end of a conversion or the A/D controller can keep track in software of when it would be appropriate to communicate to the A/D again. Once it has been determined that the A/D has completed a conversion another instruction can be transmitted to the A/D. The data from this conversion can be accessed when the next instruction is issued to the A/D.

#### **TABLE 8. Status Register**

| Status<br>Bit<br>Location | DB0         | DB1          | DB2       | DB3       | DB4         | DB5         | DB6          | DB7                    | DB8         |

|---------------------------|-------------|--------------|-----------|-----------|-------------|-------------|--------------|------------------------|-------------|

| Status<br>Bit             | PU          | PD           | Cal       | 8 or 9    | 12 or 13    | 16 or 17    | Sign         | Justification          | Test Mode   |

|                           | [           | Device Statu | S         |           | D           | O Output Fo | ormat Status |                        |             |

|                           | "High"      | "High"       | "High"    | "High"    | "High"      | "High"      | "High"       | When "High", the       | When        |

|                           | indicates a | indicates a  | indicates | indicates | indicates a | indicates a | indicates    | conversion result will | "High", the |

|                           | Power Up    | Power        | an        | an 8- or  | 12- or      | 16- or      | that the     | be output MSB first.   | device is   |

|                           | State       | Down         | Auto-Cal  | 9-bit     | 13-bit      | 17-bit      | sign bit is  | When "Low", the        | in test     |

| Function                  |             | State        | Sequence  | format    | format      | format      | included.    | result will be output  | mode.       |

|                           |             |              | is in     |           |             |             | When         | LSB first.             | When        |

|                           |             |              | progress  |           |             |             | "Low", the   |                        | "Low", the  |

|                           |             |              |           |           |             |             | sign bit is  |                        | device is   |

|                           |             |              |           |           |             |             | not          |                        | in user     |

|                           |             |              |           |           |             |             | included.    |                        | mode.       |

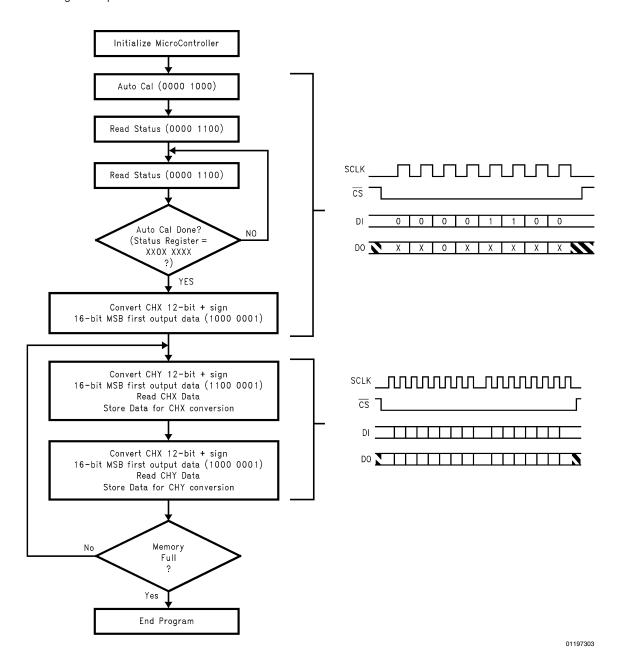

## 2.0 General Flow Chart for a Microcontroller Interface

Below is a flow chart that can be used for a microcontroller interface to the ADC12038. The data required by the ADC12038 is given in parentheses.

The timing diagrams shown to the right are suggested for each instruction issued to the ADC.

FIGURE 3. ADC12038 Program Flow Chart and Timing

#### 3.0 Examples of Microcontroller Hardware Implementations

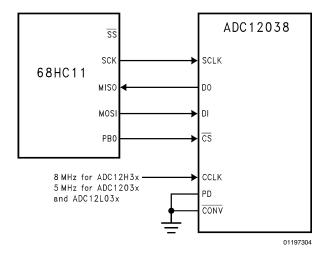

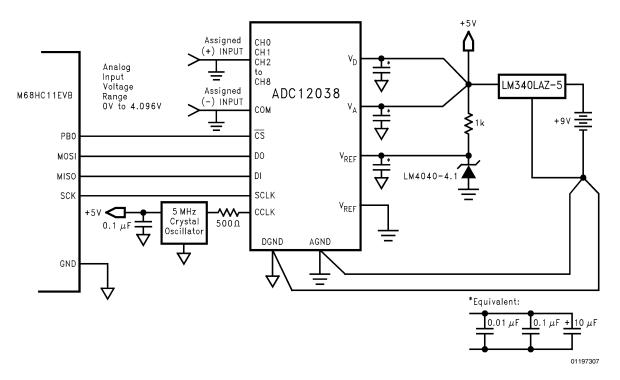

#### 3.1 THE 68HC11

Figure 4 shows the hardware interface to a Motorola M68HC11 microcontroller. Motorola's SPI (Serial Peripheral Interface) SCK, MISO, and MOSI lines are directly tied to the SCLK, DO and DI of the ADC12038. Port B bit 0 is used to generate the  $\overline{\text{CS}}$  to the ADC.

FIGURE 4. 68HC11 ADC12038 Hardware Interface

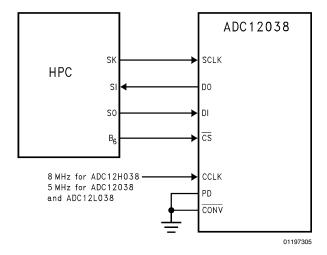

#### 3.2 NATIONAL'S HPC AND COP

The serial I/O for these devices is configured to comply with the NSC MICROWIRE™ serial data exchange standard for easy interface to the COPS™ and HPC™ families of controllers. The output data format is software-programmable, making the serial interface extremely flexible and an ideal choice for many applications. Shown in *Figure 5* is an implementation of an National Semiconductor HPC microcontroller interface. The SK (Serial clocK), SI (Serial Input data) and SO (Serial Output data) lines of the HPC, used in Nationals MICROWIRE interface, are tied directly to the ADC12038. Port B, bit 6 is used to generate a  $\overline{\text{CS}}$  for the ADC.

FIGURE 5. HPC to ADC12038 Hardware Interface

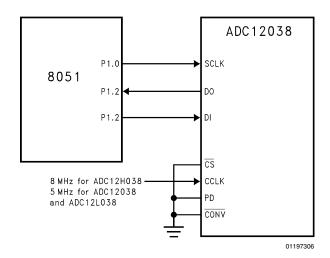

#### 3.3 THE 8051

Figure 6 shows the ADC12038 connected to an Intel 8051. The 8051 serial interface does not support the protocol of the serial interface for this device. Therefore three port lines from the 8051 (P1.0, P1.1 and P1.2) can be used to talk to the ADC. The software toggles these lines directly to form the signals necessary to control the ADC.

FIGURE 6, 8051 ADC12038 Hardware Interface

#### 4.0 68HC11 SPI Interface

This section will describe in detail an SPI interface to the ADC12038. *Figure 7*, shown below, is a detailed schematic of the interface. The Motorola M68HC11EVB evaluation board was used to verify the program included at the end of this section. Therefore, the schematic shown here shows the connections required to the 68HC11 evaluation board.

# 4.1 68HC11 SPI PORT AND REGISTER INITIALIZATION FOR THE ADC12038

The 68HC11 SPI (Serial Peripheral Interchange) interface is ideal for driving the ADC12038. The SCK, MISO, and MOSI lines of the SPI tie directly to the SCLK, DO and DI lines of the ADC.  $\overline{\text{CS}}$  for the ADC is generated using a line of the 68HC11's output port B. Here is a brief overview of the 68HC11 ports and registers used by the SPI.

The 68HC11 has four I/O ports. Port D can be set up as a general purpose I/O port or it can be used for the SPI interface and SCI (Serial Control Interface). The signal assignments for port D when used for SPI or SCI follow:

| PD7 | PD6 | PD5 | PD4 | PD3  | PD2  | PD1 | PD0 |

|-----|-----|-----|-----|------|------|-----|-----|

| Χ   | Χ   | SS  | SCK | MOSI | MISO | TXD | RXD |

SS (Slave Select), SCK (Serial ClocK), MOSI (Master Output Slave Input), MISO (Master Input Slave Output) are used for the SPI. SCI uses TXD and RXD.

There are two registers in the 68HC11 that need to be initialized: the DDRD (Data Direction Register for port D) and the SPCR (Serial Peripheral Control Register).

#### 4.1.1 DDRD

If ones are placed in the locations corresponding to the signal assignments for port D, those signals will be selected as outputs (except for the SS location). A one placed in the SS location disables that function. The SS input can be used for synchronizing master/slave communications between 68HC11s on the SPI bus. If SS is enabled and the 68HC11 is set as master then the SS input should be hard wired to a logical "high" for our case. Shown below is the data required to initialize DDRD for the ADC12038 interface. SS is disabled; SCK and MOSI are set as outputs; MISO is set as an

input. TXD and RXD are not used but are set as input and output.

| PD7 | PD6 | PD5 | PD4 | PD3 | PD2 | PD1 | PD0 |

|-----|-----|-----|-----|-----|-----|-----|-----|

| Χ   | Χ   | 1   | 1   | 1   | 0   | 1   | 0   |

DDRD resides at address i009. On the 68HC11 development board this address is 1009. All register addresses on the development board start at 1000. 0000 through 0FFF are used by the software that controls the development board. In an actual system the registers can be remapped to any 4k boundary by software.

FIGURE 7. Detailed Schematic of ADC12038 to M68HC11EVB Interface

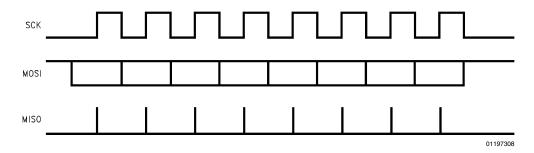

#### 4.1.2 SPCR

On power up the SPI is disabled. The data stored in the SPCR (Serial Peripheral Control Register) controls how the SPI functions. SPCR resides at address 1028 for the development board. The table below summarizes the functions of the bits in this register. The SPIE (Serial Peripheral Interrupt Enable) bit when set to 1 allows the use of an interrupt to signal when an I/O exchange has completed. The SPE (Serial Peripheral Enable) bit when set to 1 enables the SPI. DWOM bit when set to 1 sets the outputs of port D to open drain. When this bit is low port D has totem pole outputs. MSTR bit controls whether this 68HC11 is a master or slave. When set to a 1 the 68HC11 is set as a master. In the slave mode SCK is an input. The CPOL and CPHA control the

inactive level of the SCK output as well as which edge of the SCK output strobes the data out or in on the MISO or MOSI pins of port D. With both these bits set low the timing is as shown in *Figure 8*.

| BIT7 | BIT6 | BIT5 | BIT4 | BIT3 | BIT2 | BIT1 | BIT0 |

|------|------|------|------|------|------|------|------|

| SPIE | SPE  | DWOM | MSTR | CPOL | СРНА | SPR1 | SPR0 |

| 0    | 1    | 0    | 1    | 0    | 0    | 0    | 0    |

The 68HC11 clocks in the data on MISO using the rising edge of SCK. Data on MOSI changes on the falling edge of SCK. This timing matches what the ADC12038 expects. SPR1 and SPR2 control the frequency of SCK as shown in *Table 9*.

**TABLE 9. SCK Frequency Control**

| XTAL<br>Frequency | Internal<br>Processor<br>Clock | SCK<br>Frequency | Internal<br>Processor<br>Clock<br>Divide by | SPR1 | SPR0 |

|-------------------|--------------------------------|------------------|---------------------------------------------|------|------|

| 8 MHz             | 2 MHz                          | 1 MHz            | 2                                           | 0    | 0    |

| 8 MHz             | 2 MHz                          | 500 kHz          | 4                                           | 0    | 1    |

| 8 MHz             | 2 MHz                          | 250 kHz          | 8                                           | 1    | 0    |

| 8 MHz             | 2 MHz                          | 125 kHz          | 16                                          | 1    | 1    |

The SPSR (SPI Status Register) logs the status of the SPI I/O interchange. The only bit that is of concern is the SPIF which when set signals that the SPI interchange is complete.

| BIT7 | BIT6 | BIT5 | BIT4 | BIT3 | BIT2 | BIT1 | BIT0 |

|------|------|------|------|------|------|------|------|

| SPIF |      |      |      |      |      |      |      |

SPDR (SPI Data Register) is an 8-bit register used to exchange input and output data on the SPI. A write to this register will initiate an SPI exchange. The data input to the 68HC11 after an SPI exchange will reside in this register. This register resides at address 1029 for the development system.

FIGURE 8. SPI Timing Diagram Required for the ADC12038

#### 4.2 68HC11 Program Listing

The following program listing follows the flow chart given in Section 2.0.

| 0002                                                                                                                                                                                                                                          | *                            | Emmi, D.                                                                        |                                                                           | 3///2                                                                                                                                                                                                       |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                                                                               |                              | Emmy De                                                                         | encon                                                                     | 3/4/93                                                                                                                                                                                                      |  |

| 0003                                                                                                                                                                                                                                          | *                            |                                                                                 |                                                                           |                                                                                                                                                                                                             |  |

| 0004                                                                                                                                                                                                                                          | *                            | ADC12                                                                           | 38 MC68HC11 SPI Ir                                                        | tertace                                                                                                                                                                                                     |  |

| 0005                                                                                                                                                                                                                                          | *                            |                                                                                 |                                                                           |                                                                                                                                                                                                             |  |

| 0006                                                                                                                                                                                                                                          | *                            |                                                                                 |                                                                           |                                                                                                                                                                                                             |  |

| 0007                                                                                                                                                                                                                                          | *                            | This p                                                                          | rogram                                                                    |                                                                                                                                                                                                             |  |

| 0008                                                                                                                                                                                                                                          | *                            | •                                                                               | 1. Initializes                                                            | the SPI interface                                                                                                                                                                                           |  |

| 0009                                                                                                                                                                                                                                          | *                            |                                                                                 |                                                                           | elf calibration                                                                                                                                                                                             |  |

| 0010                                                                                                                                                                                                                                          | *                            |                                                                                 |                                                                           |                                                                                                                                                                                                             |  |

|                                                                                                                                                                                                                                               |                              | 3. Fills memory locations C200-C2FF with                                        |                                                                           |                                                                                                                                                                                                             |  |

| 0011                                                                                                                                                                                                                                          |                              | conversions of CHO and CH1 set up as single ended,                              |                                                                           |                                                                                                                                                                                                             |  |

| 0012                                                                                                                                                                                                                                          | *                            | 12-bit +sign MSB first                                                          |                                                                           |                                                                                                                                                                                                             |  |

| 0013                                                                                                                                                                                                                                          | *                            |                                                                                 |                                                                           |                                                                                                                                                                                                             |  |

| 0014**********                                                                                                                                                                                                                                | *****                        | *****                                                                           | ******                                                                    | *******                                                                                                                                                                                                     |  |

| 0015                                                                                                                                                                                                                                          | *                            |                                                                                 |                                                                           |                                                                                                                                                                                                             |  |

| 0016 0081                                                                                                                                                                                                                                     | CH0CONV                      | EQU                                                                             | %10000001                                                                 | ADC DI FOR CHO CONVERSION                                                                                                                                                                                   |  |

| 0017 00c1                                                                                                                                                                                                                                     | CH1CONV                      | EQU                                                                             | %11000001                                                                 | ADC DI FOR CH1 CONVERSION                                                                                                                                                                                   |  |

| 0018 0008                                                                                                                                                                                                                                     | CAL                          | EQU                                                                             | \$08                                                                      | ADC DI FOR CALIBRAITON                                                                                                                                                                                      |  |

| 0019 000c                                                                                                                                                                                                                                     | STATUS                       | EQU                                                                             | \$0C                                                                      | ADC DI FOR STATUS READ                                                                                                                                                                                      |  |

|                                                                                                                                                                                                                                               |                              |                                                                                 |                                                                           |                                                                                                                                                                                                             |  |

| 0020 clff                                                                                                                                                                                                                                     | STARTDATA                    |                                                                                 | \$C1FF                                                                    | START ADDRESS - 1 FOR CONVERSION RESULTS                                                                                                                                                                    |  |

| 0021 c2ff                                                                                                                                                                                                                                     |                              | EQU                                                                             | \$C2FF                                                                    | END ADDRESS FOR CONVERSION RESULTS                                                                                                                                                                          |  |

| 0022 1009                                                                                                                                                                                                                                     | DDRD                         | EQU                                                                             | \$1009                                                                    | DATA DIRECTION REGISTER ADDRESS                                                                                                                                                                             |  |

| 0023 1028                                                                                                                                                                                                                                     | SPCR                         | EQU                                                                             | \$1028                                                                    | SPI CONTROL REGISTER ADDRESS                                                                                                                                                                                |  |

| 0024 1029                                                                                                                                                                                                                                     | SPSR                         | EQU                                                                             | \$1029                                                                    | SPI STATUS REGISTER ADDRESS                                                                                                                                                                                 |  |

| 0025 102a                                                                                                                                                                                                                                     | SPDR                         | EQU                                                                             | \$102A                                                                    | SPI DATA REGISTER ADDRESS                                                                                                                                                                                   |  |

| 0026 1004                                                                                                                                                                                                                                     | PORTB                        | EQU                                                                             | \$1004                                                                    | PORT B ADDRESS                                                                                                                                                                                              |  |

| 0027 1008                                                                                                                                                                                                                                     | PORTD                        | EQU                                                                             | \$1008                                                                    | PORT D ADDRESS (SPI OUTPUT)                                                                                                                                                                                 |  |

| 0027 1008                                                                                                                                                                                                                                     | LONID                        | 740                                                                             | 71000                                                                     | TOWL D UNDURED PLIT OUTLOIT                                                                                                                                                                                 |  |

|                                                                                                                                                                                                                                               |                              |                                                                                 |                                                                           |                                                                                                                                                                                                             |  |

| 0029                                                                                                                                                                                                                                          |                              |                                                                                 |                                                                           |                                                                                                                                                                                                             |  |

| 0030 c000                                                                                                                                                                                                                                     |                              | ORG                                                                             | \$C000                                                                    | STARTING ADDRESS OF PROGRAM*                                                                                                                                                                                |  |

| 0031                                                                                                                                                                                                                                          |                              |                                                                                 |                                                                           |                                                                                                                                                                                                             |  |

| 0032                                                                                                                                                                                                                                          |                              |                                                                                 |                                                                           |                                                                                                                                                                                                             |  |

| 0033                                                                                                                                                                                                                                          |                              |                                                                                 |                                                                           |                                                                                                                                                                                                             |  |

| 0034                                                                                                                                                                                                                                          |                              |                                                                                 |                                                                           |                                                                                                                                                                                                             |  |

| 0035                                                                                                                                                                                                                                          |                              |                                                                                 |                                                                           |                                                                                                                                                                                                             |  |

|                                                                                                                                                                                                                                               |                              |                                                                                 |                                                                           |                                                                                                                                                                                                             |  |

| 0036                                                                                                                                                                                                                                          | *****                        |                                                                                 |                                                                           |                                                                                                                                                                                                             |  |

|                                                                                                                                                                                                                                               | ******                       | TNITTTA                                                                         | TIRE ON THEREN                                                            | TE DODE                                                                                                                                                                                                     |  |

| 0037                                                                                                                                                                                                                                          | *                            | INITIA                                                                          | LIZE SPI INTERFAC                                                         | CE PORT                                                                                                                                                                                                     |  |