# **Bumped Die (Flip Chip) Packages**

National Semiconductor Application Note 1281 April 2004

### **Table of Contents**

| Introduction and Package Construction          |

|------------------------------------------------|

| Flip Chip on Substrate Assembly Considerations |

| Substrate Land Pattern Layout Considerations   |

| Rework                                         |

Microfil is a trademark of National Semiconductor Corporation

# Introduction and Package Construction

Bumped Die products have the following features:

- 1. Requires underfill material.

- 2. Interconnect layout at fine (≤ 0.250 mm) pitch.

Bumped die products have solder bumps located on the active side of silicon IC. Bumped die products are available in (560  $\mu m)$  22 mil wafer thickness. Bump size and pitch depends on the individual product device. Bumped die products are manufactured using standard wafer fabrication process, deposition of solder bumps on i/o pads, backlapping, testing using wafer sort platform, wafer backside laser marking, singulation and packing in tape and reel and/or waffle pack.

These devices are to be mounted on substrate using techniques used for typical flip-chip applications.

Assembly process for mounting on substrate and reliability thereafter has not been characterized by National Semiconductor Corporation.

## Flip Chip on Substrate Assembly Considerations

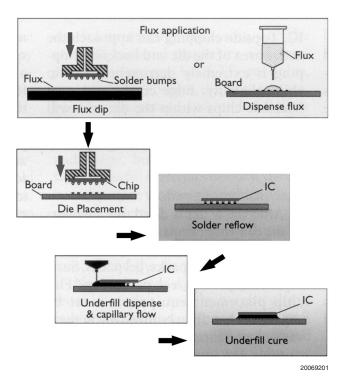

Bumped die flip chip assembly operations include,

- Component placement using flip chip mounting/ placement equipment.

- The placement step involves application of flux to the solder bumps either using a spray fluxing arrangement or a flux-dip station on the pick-and-place machine.

- An alternative method using no-flow or flux underfill may also be used for assembly.

- 4. Flux dip should involve wetting of at least 1/3 of the total bump height with flux.

- Standard reflow (convection preferred) to form solder joint interconnections.

- 6. Cleaning step (depending on type of flux used).

- 7. Underfill application using typical underfill equipment.

- 8. Figure 1 illustrates the process steps involved.

FIGURE 1. Summary of Flip-chip Assembly Process

# **Substrate Land Pattern Layout Considerations**

For flip-chip type applications, there are multiple options available for pad geometry on PCB.

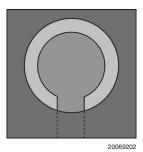

- Non-solder mask defined or pad defined is the preferred pad layout. However lower pitches may not utilize this layout due to PCB limitations. Refer to Figure 2.

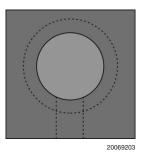

- Solder mask defined (individual pad locations are available with mask separating adjacent pad locations). Refer to Figure 3.

- Trench-over-trace openings, where continuous trenches in solder mask are used to define the entire row (or

- multiple rows) of pad locations (where the pads themselves are actually part of the trace itself). Refer to Figure 4.

- The trench-type design may involve traces passing through the trench or traces ending in the trench itself (both types can be used, however, traces ending in the trench are preferred).

- Total solderable area available on the PCB pads should be approximately 75 to 100% of area of the solder bump cross-section

Other considerations include:

# **Substrate Land Pattern Layout Considerations** (Continued)

- A copper layer thickness of 1/2 oz. (17µ) is recommended. Finer pitches are preferred to be used with thinner copper layers to maintain a reasonable solder joint stand-off.

- Stand-off achieved should allow easy flow of underfill epoxy underneath the die. Min stand-off required is dependent on the flow characteristics of the underfill being used.

- 3. Underfill selection is largely dependent on the bump pitch being used and the corresponding stand-off (solder

- joint height after assembly on PCB) achieved. Lower stand-off assemblies require the use of underfills with superior flow characteristics.

- 4. Via-in-pad structures (micro-via in bump pad) are not preferred for the pitches typical to bumped die flip-chips.

- Organic solderability preservative coating (OSP) as well as Nickel-Gold pad finish can be used for PCB assembly.

- For Nickel-Gold (electroplated Nickel, immersion Gold) gold thickness should be less than 0.5 microns.

- 7. HASL (Hot Air Solder Leveled) board finish with these package types is not allowed.

FIGURE 2. Non-Solder-Mask-Defined Pad Layout on PCB

FIGURE 3. Solder-Mask-Defined Pad Layout on PCB

FIGURE 4. Trench-type pad opening (through-trace type)

### Rework

Reworkability of the assembly is entirely dependent on the underfill used. Rework of assembled die/flip chip before

underfilling is started is possible using standard rework equipment.

# **AN-1281**

### **Notes**

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

**National Semiconductor** Americas Customer Support Center Email: new.feedback@nsc.com

Tel: 1-800-272-9959

www.national.com

**National Semiconductor Europe Customer Support Center**

Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

**National Semiconductor** Asia Pacific Customer Support Center Email: ap.support@nsc.com **National Semiconductor** Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560