## LVDS Timing DS32ELX0421 and DS32ELX0124 Serializers and Deserializers

National Semiconductor Application Note 1979 Nate Unger July 2, 2009

#### Introduction

The highly integrated FPGA-Link SerDes chipset (DS32ELX0421 and DS32ELX0124) enables low-cost FPGAs in a variety of high performance, high speed applications. They feature advanced on-chip signal and clock conditioning circuitry that extends the data transmission reach of CAT-6 (shielded 24 AWG) cable beyond 20 meters without additional external components.

The Serializer and Deserializer unique architecture is designed specifically to address the interface requirements of low cost FPGA devices. The 5-bit LVDS parallel data interface simplifies board layout by reducing the number of input/output (I/O) pins and traces between the Serializer, Deserializer and the FPGA. This application note explains the Serializer and Deserializer LVDS timing requirements for the DS32EL0421, DS32EL0124, DS32ELX0421 and the DS32ELX0124 products.

#### Serializer Device Timing Requirements

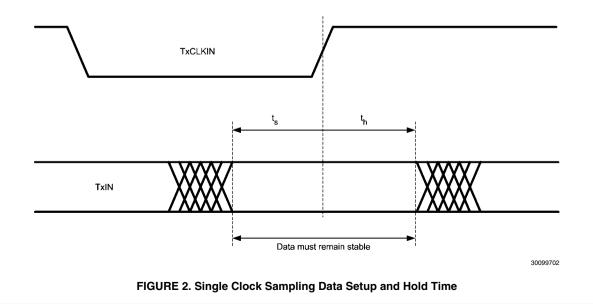

If you think back to how the Channel Link Serializers (e.g. DS90CR483A) are specified, there is a single clock edge

sampling a single data edge on the LVCMOS parallel interface. The clock samples the data on a single edge. The setup time of 2.5 nanoseconds and hold times are 0 seconds. The optimal clock position for the Channel Link Serializer is in the middle of the bit period of the data, as seen in *Figure 2*.

AN-1979

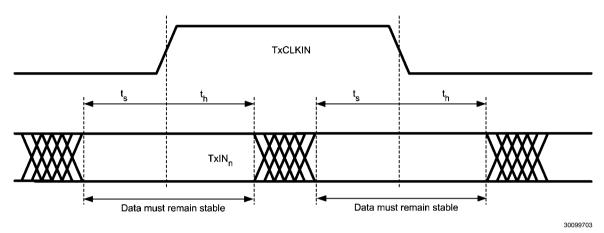

For Dual Data Rate (DDR) interfaces, the clock samples the data on both edges of the clock. CMOS, LVPECL or LVDS interfaces can utilize a DDR interface. The main advantage of DDR interfaces is the clock and data frequency are identical which maximizes data throughput for the protocol. The duty cycle distortion of the clock plays a critical part in the setup and hold time as both edges must meet the setup and hold time requirements to sample the data in the mid-bit transition.

Note that if there is skew between the various data lines, or if there is duty cycle distortion of the clock, all of these nonidealities work to reduce the amount of timing margin in the system, so all effort should be taken to reduce inter-pair data skew and clock distortion.

FIGURE 3. DDR Interface Setup and Hold Time

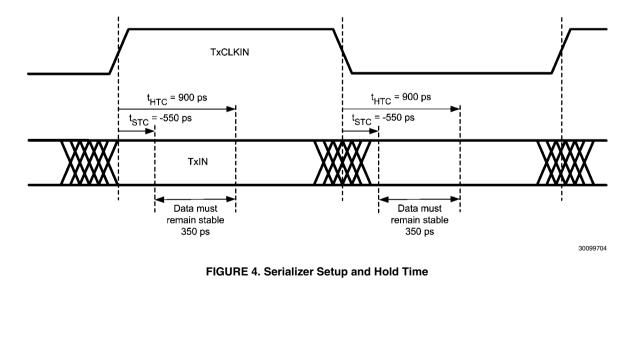

The LVDS DDR input implementation in the Serializer reduces the number of Clock / PLL resources required in the host FPGA. The setup and hold time requirements for the LVDS Interface input latch expects the alignment of the clock and data transitions. An additional clock resource is not needed to offset the clock edges in the middle of the data bits.

The numbers that are specified in the datasheet (minimum setup time is -550 ps and the maximum hold time is 900 ps) are worst case numbers and by assuring that each of your data lines meets these timing requirements, you are guaran-

teeing that the device will properly latch it's input data. A negative setup time comes about because within the device there is a delay on the clock line that allows the FPGA to shift out the clock and data on the same clock edge. Internal to the Serializer, the clock is shifted to sample the data. When the clock transitions, the actual data that is sampled is the data that was on the input pins a few hundred ps earlier. A graphical explanation of these timings is shown in the *Figure 4* and shows a sampling window of 350 ps.

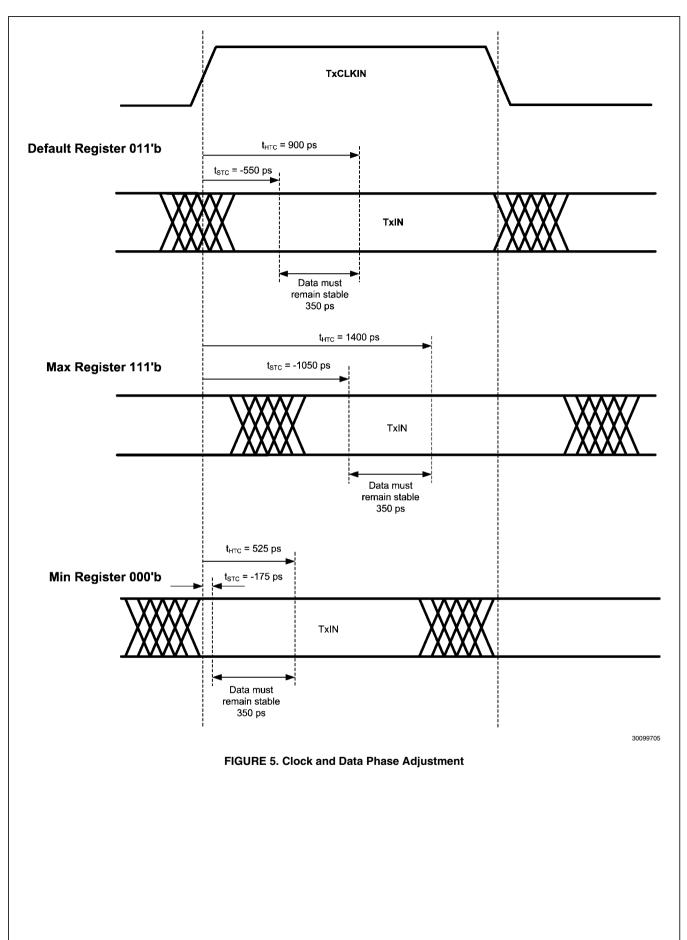

### **Serializer Register Programmability**

The clock to data delay can be optimized by programming register bits in the Serializer. This feature allows adjustment of the Serializer Setup and Hold time locations to be optimized to the Data Valid time provided by the FPGA host device. To adjust the Serializer clock and data delay use register 0x30 bits [7:5]. The default delay between the clock and data is 725 ps (value 011'b). Each LSB changes the delay by 125 ps which gives a range in delay from 350 ps to 1225 ps. See *Table 1* and *Figure 5*.

| Register Setting<br>Reg 0x30<br>bits [7:5] | Sample Time<br>Instant<br>(ps) | Setup Time<br>(ps) | Hold Time<br>(ps) | Data Valid<br>(ps) |

|--------------------------------------------|--------------------------------|--------------------|-------------------|--------------------|

| 000'b                                      | 350                            | – 175              | 525               | 350                |

| 001'b                                      | 475                            | - 300              | 650               | 350                |

| 010'b                                      | 600                            | - 425              | 775               | 350                |

| 011'b *                                    | 725                            | - 550              | 900               | 350                |

| 100'b                                      | 850                            | - 675              | 1025              | 350                |

| 101'b                                      | 975                            | - 800              | 1150              | 350                |

| 110'b                                      | 1100                           | - 925              | 1275              | 350                |

| 111'b                                      | 1225                           | - 1050             | 1400              | 350                |

**AN-1979**

### Deserializer Device Timing Requirements

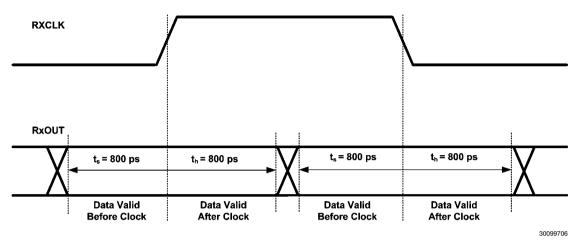

For the Deserializers (DS32EL0124 and DS32ELX0124) the LVDS clock and data outputs are skewed to provide maximum setup and hold durations for the target FPGA. Further examination of the datasheet reveals the setup and hold times

are 800 ps, centering the clock and data at a maximum line rate.

For example at a maximum line rate of 3.125 Gbps, the LVDS clock rate is 312.5 MHz or 3.2 ns. Divide this by 2 due to the DDR clocking and the data period is 1.6 ns. A setup and hold time at 800 ps puts the clock transition in the mid-bit transition of the data as shown in *Figure 6*.

FIGURE 6. Deserializer (Setup and Hold Time) Data Valid Times

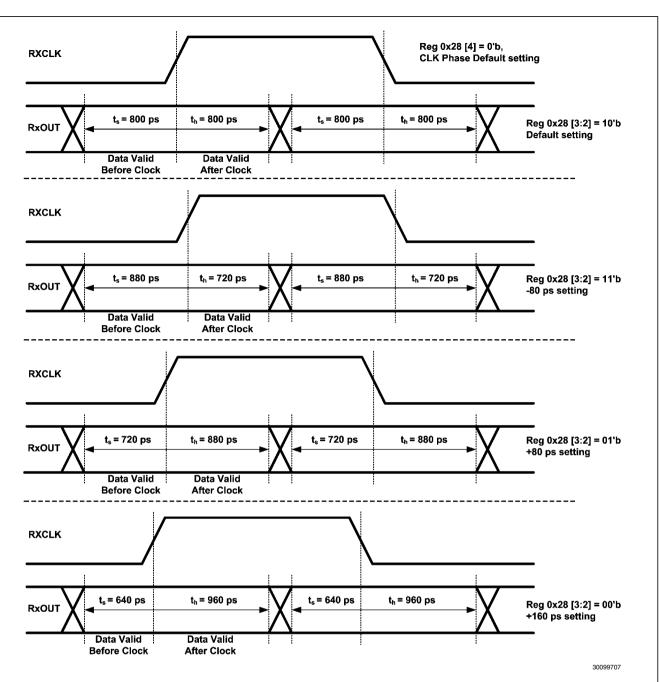

### Deserializer Register Programmability

Like the Serializer, the Desierializer can also be optimized to adjust the clock edge location to be compatible with the downstream device's input timing requirement. To adjust the Deserializer, use register 0x28. Bits 2 and 3 of register 0x28 adjust the phase in 80 ps steps which gives 240 ps adjustment. The default value of register 0x28 is 10'b for an 800 ps setup and hold time. The time can be adjusted to a minimum of 640 ps and a maximum of 880 ps. The Data Valid After Clock (Hold) can be set from 960 ps to 720 ps.

The clock phase can also be inverted by bit 4 of register 0x28. See *Table 2* and *Figure 7*.

| Register Setting<br>Reg 0x28<br>bits [3:2] | Offset<br>(ps) | Data Valid<br>Before Clock<br>(ps) | Data Valid<br>After Clock<br>(ps) |

|--------------------------------------------|----------------|------------------------------------|-----------------------------------|

| 00'b                                       | 160            | 640                                | 960                               |

| 01'b                                       | 80             | 720                                | 880                               |

| 10'b *                                     | 0              | 800                                | 800                               |

| 11'b                                       | - 80           | 880                                | 720                               |

FIGURE 7. Deserializer (Setup and Hold Time) Data Valid Times Programability

#### Conclusion

In summary, the DDR timing of the FPGA-Link Serializers and Deserializers have been optimized for use with FPGAs. Further, adjustability of the delay between the clock and data allows the user to configure the sampling window or the clock edge to optimize it for specific FPGA requirements.

### **Referenced Parts**

This application note refers to DS32EL0421, DS32EL0124, DS32ELX0421, DS32ELX0124

# Notes

| Products                       |                              | Design Support                  |                                |  |

|--------------------------------|------------------------------|---------------------------------|--------------------------------|--|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH® Tools                  | www.national.com/webench       |  |

| Audio                          | www.national.com/audio       | App Notes                       | www.national.com/appnotes      |  |

| Clock and Timing               | www.national.com/timing      | Reference Designs               | www.national.com/refdesigns    |  |

| Data Converters                | www.national.com/adc         | Samples                         | www.national.com/samples       |  |

| Interface                      | www.national.com/interface   | Eval Boards                     | www.national.com/evalboards    |  |

| LVDS                           | www.national.com/lvds        | Packaging                       | www.national.com/packaging     |  |

| Power Management               | www.national.com/power       | Green Compliance                | www.national.com/quality/green |  |

| Switching Regulators           | www.national.com/switchers   | Distributors                    | www.national.com/contacts      |  |

| LDOs                           | www.national.com/ldo         | Quality and Reliability         | www.national.com/quality       |  |

| LED Lighting                   | www.national.com/led         | Feedback/Support                | www.national.com/feedback      |  |

| Voltage Reference              | www.national.com/vref        | Design Made Easy                | www.national.com/easy          |  |

| PowerWise® Solutions           | www.national.com/powerwise   | Solutions                       | www.national.com/solutions     |  |

| Serial Digital Interface (SDI) | www.national.com/sdi         | Mil/Aero                        | www.national.com/milaero       |  |

| Temperature Sensors            | www.national.com/tempsensors | SolarMagic™                     | www.national.com/solarmagic    |  |

| Wireless (PLL/VCO)             | www.national.com/wireless    | PowerWise® Design<br>University | www.national.com/training      |  |

For more National Semiconductor product information and proven design tools, visit the following Web sites at:

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

#### Copyright© 2009 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959

National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com

www.national.com