DECEMBER 1976

Manuel Mere

Jonathan Stinehelfer

National Semiconductor Corp.

## Pulsed Power Supply Operation of Selected MM2102 Static RAM

## introduction

Static RAMs have a significant number of advantages over dynamic devices, including ease of use and no requirement for refresh. One disadvantage of static RAMs is that they dissipate more power on a per bit basis than dynamic RAMs. This application note will describe a technique by which selected MM2102 Static RAMs can be operated in a standby mode with a very low average power drain.

The SM61480 is an MM2102 that has been selected to ensure operation in the pulsed power mode.

## theory of operation

The MM2102 is manufactured using N-channel enhancement mode technology which is key to operation in a pulsed  $V_{\rm CC}$  mode. An enhancement mode device conducts current when the gate is a threshold voltage (approximately 1 volt) above that of the source. Once the voltage between the gate and the source is less than the threshold voltage the device is cut off and no current conduction can take place. This characteristic allows data stored in the memory cell to be maintained for short periods of time with the power supply off.

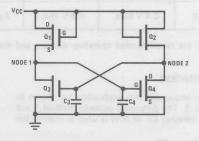

To better understand how data is maintained, consider the MM2102 memory cell (figure 1). Assume the device has been operating in the normal mode (V $_{\rm CC}$  applied) and that node 1 is high and node 2 is low. Capacitor C $_{\rm 4}$  will be charged to a value near V $_{\rm CC}$  and capacitor C $_{\rm 3}$  will be charged to a value near ground.

When V<sub>CC</sub> falls, two things happen in the storage cell:

- 1.  $Q_1$  starts turning off as  $V_{CC}$  (and the gate) begin to fall.

- 2. Q2 will turn off when VCC falls below its threshold.

With  $Q_1$  and  $Q_2$  off, the cell is now in a stable condition and will remain stable until the leakage currents discharge  $C_4$  below the trip point of the flip-flop. The charge on the capacitor can be maintained above the trip point by replenishing  $C_4$  on a periodic basis. The replenishing during power-up brings node 1 back to its initial condition each time. The pulsed power mode can be continued indefinitely, resulting in a very low average power drain.

FIGURE 1. MM2102 Memory Cell

FIGURE 2. Method 1

FIGURE 3. Method 2

|          | V <sub>CC</sub> Low | V <sub>CC</sub> High | Ton  | T <sub>OFF</sub>                  | CE         | R/W        |

|----------|---------------------|----------------------|------|-----------------------------------|------------|------------|

| Scheme 1 | 0.4 V Max.          | 4.5 V Min.           | 2 μs | 2000 μs at 25°C<br>200 μs at 70°C | Don't Care | 2.4 V Min. |

| Scheme 2 | 0.4 V Max.          | 4.5 V Min.           | 2 μs | 2000 μs at 25°C<br>200 μs at 70°C | 2.4 V Min  | Don't Care |

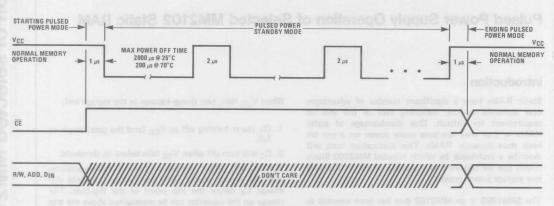

Table I gives the recommended operating voltages and timings for the two different schemes.

## implementation

Two ways to implement this application are shown in figures 2 and 3. The difference between method 1 and method 2 is whether  $\overline{\text{CE}}$  or R/W is used to control the memory.

R/W method 1, or  $\overline{\text{CE}}$  method 2, should be brought to the 2.4 volt level at least 1  $\mu s$  prior to the start of the pulsed operation. Once the pulsed mode has ended and the V<sub>CC</sub> supply has been brought back to its guaranteed

operating range, a hold time of at least 1  $\mu s$  is required before memory operation is attempted. See table I.

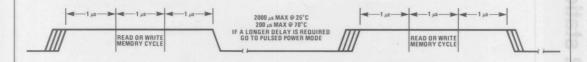

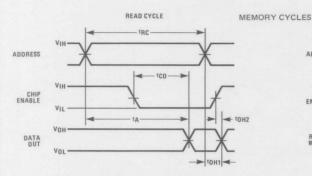

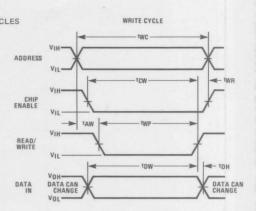

Figure 4 illustrates the timing required for powering the memory up for a memory cycle then powering the memory down until the next memory cycle is required or the maximum allowed time for power down is reached. If the next memory cycle is not required within the maximum time allowed for power-down, power-up pulses can be used — this is a combination of the techniques illustrated in figures 2 or 3 and figure 4.

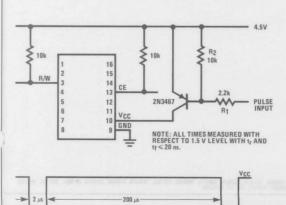

Note: All times measured with respect to 1.5 V level with  $t_{\text{r}}$  and  $t_{\text{f}} \leqslant 20 \, \text{ns}.$

FIGURE 4.

Figure 5 illustrates a pulse power circuit suitable for operating an enhancement mode MM2102 RAM. The pulse input can come from any TTL output that can sink at least 2 mA. If the pulse input is driven with a CMOS output,  $\rm R_2$  is not necessary as the  $\rm V_{OH}$  of a CMOS part will turn the pass transistor (2N3467) off without a pullup resistor. A 74C902 is a CMOS device that is a good driver for this application.

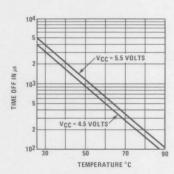

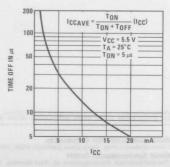

Figures 6 and 7 show typical characteristics for  $\rm t_{off}$  vs temperature and  $\rm I_{CCAVE}$  vs duty cycle.

FIGURE 5. Pulse Power Circuit

FIGURE 6. TOFF vs Temperature

FIGURE 7. ICCAVE VS TOFF