## LMV1091 Noise Suppression Microphone Amplifier Evaluation Kit User's Guide

National Semiconductor Application Note 1989 Gerardine Ly November 12, 2009

### **Overview**

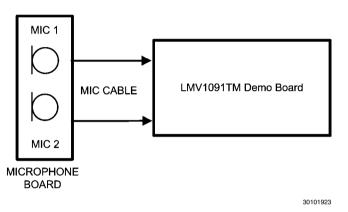

The LMV1091TL evaluation kit contains the following:

- LMV1091TL Demonstration Board, 551600341–001

- Microphone board

- Microphone cable

#### FIGURE 1. Basic Evaluation System

#### Introduction

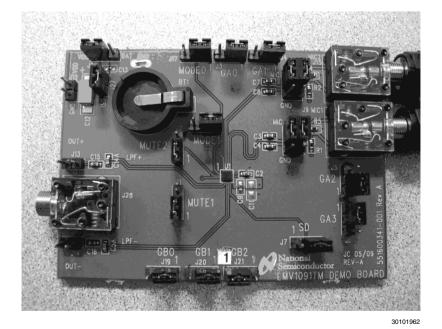

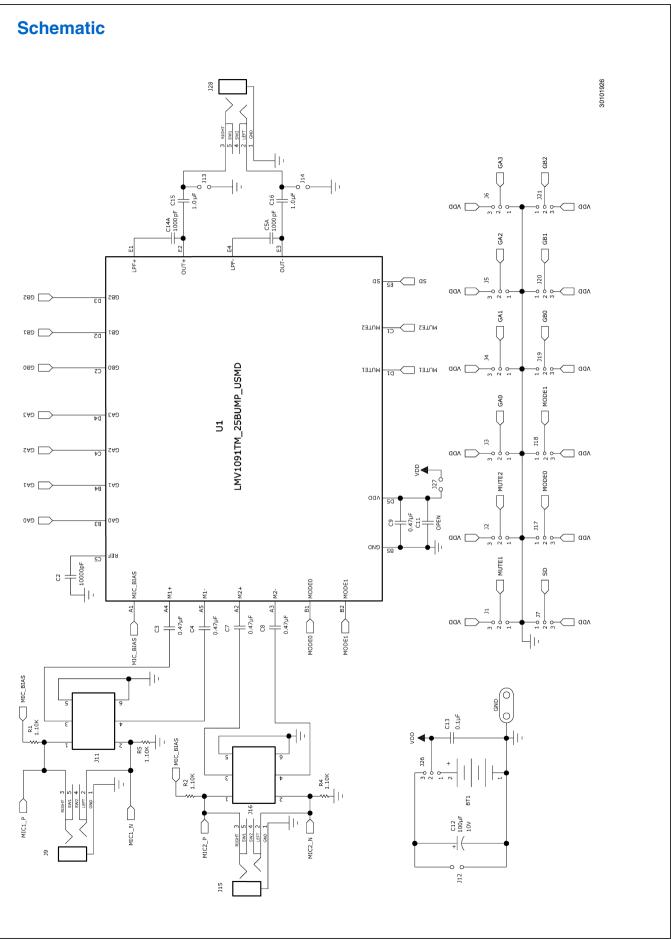

The LMV1091 demo board offers the means for easy evaluation of the LMV1091 Dual input, Far Field Noise Suppression (FFNS) Microphone Amplifier with Differential Outputs.

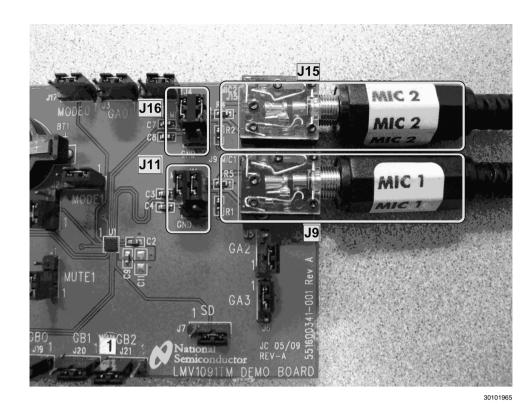

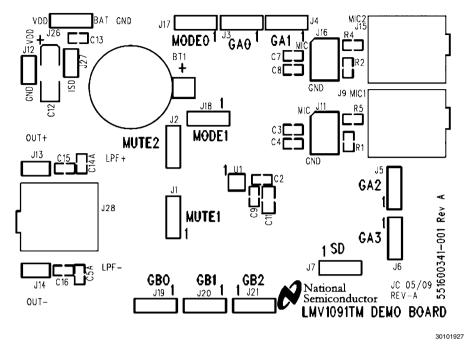

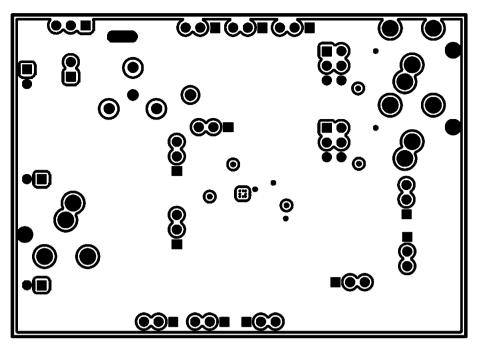

FIGURE 2. The LMV1091TL Demo Board

AN-1989

# AN-1989

### **General Description**

The LMV1091 is a fully analog dual input, differential output, microphone array amplifier designed to reduce background acoustic noise, while delivering superb speech clarity in voice communications applications. The LMV1091 has two differential input microphone amplifier channels plus far-field noise suppression (FFNS) circuitry. The LMV1091 preserves near-field wire signals within 4cm of the microphones. While rejecting far-field acoustic noise greater than 50cm from the microphones. Up to 20dB of far-field rejection is possible in a properly configured and using  $\pm 0.5$ dB matched microphones.

## **Operating Conditions**

- Temperature Range

- Power Supply Voltage

- I<sup>2</sup>C supply voltage

$\begin{array}{c} -40^{\circ}\text{C} \leq \text{T}_{\text{A}} \leq 85^{\circ}\text{C} \\ 2.7\text{V} \leq \text{V}_{\text{DD}} \leq 5.5\text{V} \\ 1.7\text{V} \leq \text{I}^{2}\text{C}\text{V}_{\text{DD}} \leq 5.5\text{V} \end{array}$

## LMV1091 Demo Board

The LMV1091TL Demonstration Board takes analog inputs from two microphones and performs the Far Field noise cancellation process. It outputs an analog differential signal. This output can be connected to a recording device, such as a personal computer sound card through its LINE IN/MIC IN input or mobile phone through its MIC IN input, for evaluation purposes.

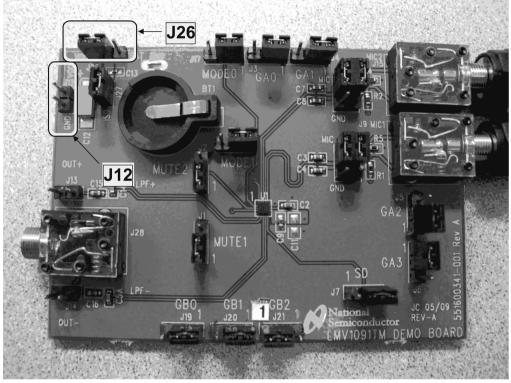

## Power Supply of the LMV1091 Demo Board

The LMV1091 demo board provides two (2) possible sources for the power supply. The first one is using the external supply via header J12 for  $V_{DD}$  and GND. Header J26 needs to be in the position shown in Figure 3.

FIGURE 3. Power Supply Connectors and Headers

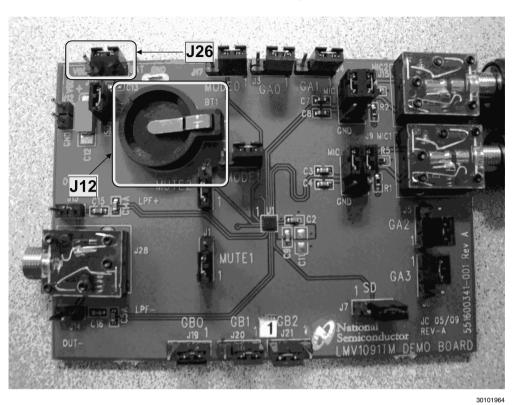

The second source of power supply is a small battery placed in battery holder mounted on the PCB. See Figure 4. For a limited time, the demo board can be operated from the board battery (CR1220 placed in the battery holder BT1). To operate the board using a battery, J26 must be configured as shown in Figure 4.

FIGURE 4. Battery Power Supply

## Connecting Microphones to the LMV1091 Demo Board

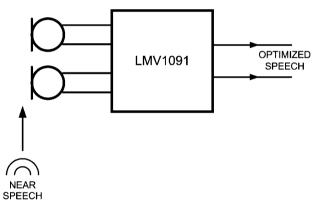

The demo board can be used to connect a set of two microphones to the LMV1091 to evaluate the performance of the LMV1091 in a customer application. To enable these microphone input connectors, the jumpers on header J11 and J16 must be placed between pin 3–5 and pin 4–6 of both headers. Microphones can also be connected to 3.5mm connectors J9 and J15 (see Figure 5). For a optimal performance of the Far Field Noise Reduction system it is important to find the correct placement of the microphones. In many applications the microphones are placed next to each other with a distance of 1.5cm to 2.5cm between the microphones. The best noise canceling performance will occur in systems where the far field signals comes from a source orthogonal to the plane of the microphones and where the desired signal is close to the microphones and is located in line with the microphones as shown in Figure 6.

FIGURE 5. Orientation of Microphones and Sound Sources

FIGURE 6. Orientation of Microphones and Sound Sources

## Microphone Placement in the Application

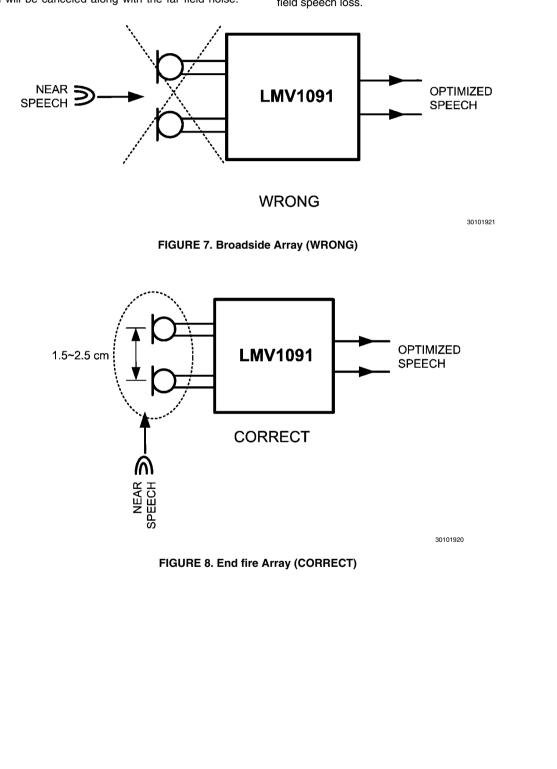

Because the LMV1091 is a microphone array Far Field Noise Reduction solution, proper microphone placement is critical for optimum performance. Two things need to be considered: The spacing between the two microphones and the position of the two microphones relative to near field source.

If the spacing between the two microphones is too small, near field speech will be canceled along with the far field noise.

Conversely, if the spacing between the two microphones is large, the far field noise reduction performance will be degraded. The optimum spacing between Mic 1 and Mic 2 is 1.5-2.5cm. This range provides a balance of minimal near field speech loss and maximum far field noise reduction. The microphones should be in line with the desired sound source 'near speech' and configured in an endfire array orientation from the sound source (see *Figure 8*). If the 'near speech' (desired sound source) is equidistant to the source like a broad-side array (see *Figure 7*) the result will be a great deal of near field speech loss.

## Pre Amp and Post Amp Gain

gain control. The Post-Amp gain can be controlled using the GB0-GB2 pins. See table 3 below for Post-amplifier gain control.

The Pre-amplifier gain of the LMV1091TM can be controlled using the GA0-GA3 pins. See table 2 below for Pre-amplifier

| GA3 | GA2 | GA1 | GA0 | Pre-Amplifier Gain |

|-----|-----|-----|-----|--------------------|

| 0   | 0   | 0   | 0   | 6dB                |

| 0   | 0   | 0   | 1   | 8dB                |

| 0   | 0   | 1   | 0   | 10dB               |

| 0   | 0   | 1   | 1   | 12dB               |

| 0   | 1   | 0   | 0   | 14dB               |

| 0   | 1   | 0   | 1   | 16dB               |

| 0   | 1   | 1   | 0   | 18dB               |

| 0   | 1   | 1   | 1   | 20dB               |

| 1   | 0   | 0   | 0   | 22dB               |

| 1   | 0   | 0   | 1   | 24dB               |

| 1   | 0   | 1   | 0   | 26dB               |

| 1   | 0   | 1   | 1   | 28dB               |

| 1   | 1   | 0   | 0   | 30dB               |

| 1   | 1   | 0   | 1   | 32dB               |

| 1   | 1   | 1   | 0   | 34dB               |

| 1   | 1   | 1   | 1   | 36dB               |

#### **TABLE 1. Mic Pre-Amp Gain Settings**

#### TABLE 2. Post-Amp Gain Settings

| GB2 | GB1 | GB0 | Pre-Amplifier Gain |

|-----|-----|-----|--------------------|

| 0   | 0   | 0   | 6dB                |

| 0   | 0   | 1   | 9dB                |

| 0   | 1   | 0   | 12dB               |

| 0   | 1   | 1   | 15dB               |

| 1   | 0   | 0   | 18dB               |

| 1   | 0   | 1   | 18dB               |

| 1   | 1   | 0   | 18dB               |

| 1   | 1   | 1   | 18dB               |

**Note:** The silkscreen on the LMV1091TM demoboard has a '1' on the header for GA0–GA3, GB0–GB2, MUTE1, MUTE2, MODE0, and MODE1. The '1' indicates GND pin.

## **Noise Reduction Mode Settings**

The LMV1091TM has four mode settings. It can be placed in noise cancellation mode, mic 1 on with mic 2 off, mic 1 off with mic 2 on, and mic1 and mic2. See Table 3. for control settings.

#### TABLE 3. Noise Reduction Mode Settings

| Mode 1 | Mode 0 | Noise Reduction Mode Selection |

|--------|--------|--------------------------------|

| 0      | 0      | Noise Cancellation mode        |

| 0      | 1      | Mic 1 On                       |

| 1      | 0      | Mic 2 On                       |

| 1      | 1      | Mic 1 + Mic 2                  |

Mic 1 and Mic 2 can be muted independently, using the Mute 1 and Mute 2 pins. See Table 4 for control settings.

#### TABLE 4. Noise Reduction Nute Settings

| Mute2 | Mute1 | Noise Reduction Mode Selection |

|-------|-------|--------------------------------|

| 0     | 0     | Mic 1 and Mic 2 on             |

| 0     | 1     | Mic 1 mute                     |

| 1     | 0     | Mic 2 mute                     |

| 1     | 1     | Mic 1 and Mic 2 mute           |

## **PCB Layout Guidelines**

This section provides general practical guidelines for PCB layouts that use various power and ground traces. Designers should note that these are only "rule-of-thumb" recommendations and the actual results are predicated on the final layout.

#### DIFFERENTIAL SIGNALS

Keep both signals coupled by routing them closely together and keeping them of equal length. Keep all impedances in both traces of the signal equal.

#### POWER AND GROUND

Connect all ground pins together under the part forming a star point. Keep the current for the de-coupling capacitor of the REF pin C4 and the accompanying ground pin B5 separated from the other currents. Keep the location of the supply decoupling capacitor close to  $V_{DD}$  pin D5 and ground.

#### Description of Headers and Connectors of the LMV1091 Demo Board The LMV1091 demo board provides many headers and conjumpers on the LMV1091 demo board is also indic

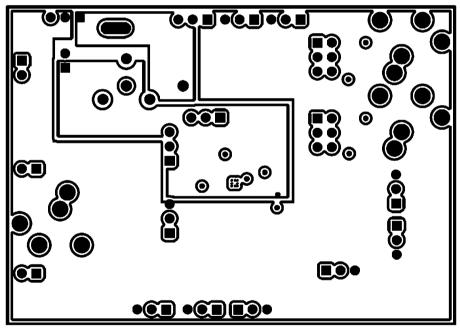

The LMV1091 demo board provides many headers and connectors for connecting test equipment and controlling the settings of the part. The function that is controlled by the jumpers on the LMV1091 demo board is also indicated on the PCB in silk screen as shown in *Figure 9* (The name in parenthesis is as shown in the silk screen).

## **Connector and Header Functions**

| Designator | Function or Use                                            | Comment                                                                                                                                               |

|------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| J12        | Power supply connector for external supply                 |                                                                                                                                                       |

| J26        | Supply select pin external ( $V_{DD}$ ) or battery (BAT)   |                                                                                                                                                       |

| J11, J16   | Connection for input of electrical test signals at pin 4+5 | Pin 3+4 differential input with ground at Pin 5+6                                                                                                     |

| J8, J10    | Low pass filter selection (LPF+, LPF-)                     | Pin 1+2 to connect to an external LPF capacitor. Pin 2+3 select the on board LPF capacitor C5, C14 (a minimum of 1nF is always mounted on the board). |

| J26        | Supply select pin external ( $V_{DD}$ ) or battery (BAT)   |                                                                                                                                                       |

| J27        | Connects Supply to V <sub>DD</sub> pin                     |                                                                                                                                                       |

| J1         | Select for MUTE1                                           |                                                                                                                                                       |

| J2         | Select for MUTE2                                           |                                                                                                                                                       |

| J3         | Select for GA0                                             |                                                                                                                                                       |

| J4         | Select for GA1                                             |                                                                                                                                                       |

| J5         | Select for GA2                                             |                                                                                                                                                       |

| J6         | Select for GA3                                             |                                                                                                                                                       |

| J7         | Select for SD                                              |                                                                                                                                                       |

| J17        | Select for MODE0                                           |                                                                                                                                                       |

| J18        | Select for MODE1                                           |                                                                                                                                                       |

| J19        | Select for GB0                                             |                                                                                                                                                       |

| J20        | Select for GB1                                             |                                                                                                                                                       |

| J21        | Select for GB2                                             |                                                                                                                                                       |

| J13, J14   | GND outputs (option to test for various parameters         |                                                                                                                                                       |

www.national.com

AN-1989

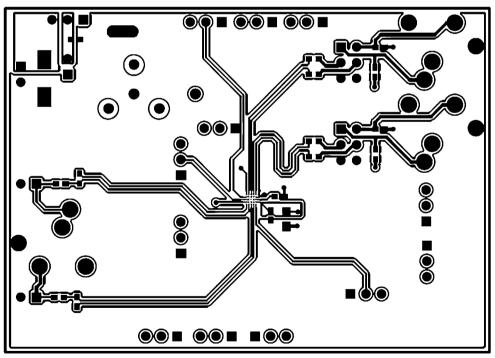

## Layout

FIGURE 9. Layout, Silk Screen

30101928

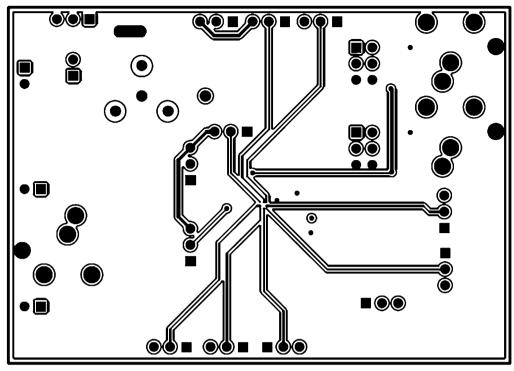

FIGURE 11. Layout, Top Inner Layer

30101924

FIGURE 12. Layout, Bottom Inner Layer

# AN-1989

FIGURE 13. Layout, Bottom Layer

| Bill of Mate                                                                                                                                                |                                                       |         |           |        |              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------|-----------|--------|--------------|

| Designator                                                                                                                                                  | Component                                             | Value   | Tolerance | Rating | Package Type |

| U1                                                                                                                                                          | LMV1091TL                                             |         |           |        |              |

| C15, C16                                                                                                                                                    | Capacitor Ceramic                                     | 1.0µF   | 10%       | 16V    | 0603         |

| C2                                                                                                                                                          | Capacitor Ceramic                                     | 10000pF | 10%       | 50V    | 0603         |

| C3, C4, C7, C8, C9                                                                                                                                          | Capacitor Ceramic                                     | 0.47pF  | 10%       | 16V    | 0603         |

| C5A, C14A                                                                                                                                                   | Capacitor Ceramic                                     | 4.7nF   | 10%       | 100V   | 0603         |

| C13                                                                                                                                                         | Capacitor Ceramic                                     | 0.1µF   | 10%       | 16V    | 0603         |

| C11                                                                                                                                                         | No Load                                               | No Load |           |        |              |

| C12                                                                                                                                                         | Capacitor Tantalum                                    | 100µF   | 10%       | 10V    | Case C       |

| R1, R2, R4, R5                                                                                                                                              | Resistor                                              | 1.1k    | 1%        | 1/10W  | 0603         |

| J12, J13, J14, J27                                                                                                                                          | Connector Header Brkway .100<br>02POS STR             |         |           |        |              |

| J11, J16                                                                                                                                                    | Connector Header Brkway .100<br>06POS VERT            |         |           |        |              |

| J9, J15, J28                                                                                                                                                | 5 Pole Headphone conn jack stereo<br>3.5mm horizontal |         |           |        |              |

| GND                                                                                                                                                         | Ground hook jumper 5mm high mount                     |         |           |        |              |

| BT1                                                                                                                                                         | Battery holder CR1220, 1 cell 12mm                    |         |           |        |              |

| J1_SH, J2_SH,<br>J3_SH, J4_SH,<br>J5_SH, J6_SH,<br>J7_SH, J11a_SH,<br>J11b_SH, J16a_SH,<br>J16b_SH, J17_SH,<br>J18_SH, J19_SH,<br>J20_SH, J21_SH,<br>J26_SH | Jumper Shunt 0.100" 30µin Au<br>(no handle)           |         |           |        |              |

| J1, J2, J3, J4, J5, J6,<br>J7, J18, J19, J20,<br>J21, J26                                                                                                   | Connector Header Brkway .100<br>03POS STR             |         |           |        |              |

## **Revision History**

| Rev | Date     | Description      |

|-----|----------|------------------|

| 1.0 | 11/12/09 | Initial release. |

For more National Semiconductor product information and proven design tools, visit the following Web sites at:

| Pr                             | oducts                       | Design Support                  |                                |

|--------------------------------|------------------------------|---------------------------------|--------------------------------|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH® Tools                  | www.national.com/webench       |

| Audio                          | www.national.com/audio       | App Notes                       | www.national.com/appnotes      |

| Clock and Timing               | www.national.com/timing      | Reference Designs               | www.national.com/refdesigns    |

| Data Converters                | www.national.com/adc         | Samples                         | www.national.com/samples       |

| Interface                      | www.national.com/interface   | Eval Boards                     | www.national.com/evalboards    |

| LVDS                           | www.national.com/lvds        | Packaging                       | www.national.com/packaging     |

| Power Management               | www.national.com/power       | Green Compliance                | www.national.com/quality/green |

| Switching Regulators           | www.national.com/switchers   | Distributors                    | www.national.com/contacts      |

| LDOs                           | www.national.com/ldo         | Quality and Reliability         | www.national.com/quality       |

| LED Lighting                   | www.national.com/led         | Feedback/Support                | www.national.com/feedback      |

| Voltage Reference              | www.national.com/vref        | Design Made Easy                | www.national.com/easy          |

| PowerWise® Solutions           | www.national.com/powerwise   | Solutions                       | www.national.com/solutions     |

| Serial Digital Interface (SDI) | www.national.com/sdi         | Mil/Aero                        | www.national.com/milaero       |

| Temperature Sensors            | www.national.com/tempsensors | SolarMagic™                     | www.national.com/solarmagic    |

| Wireless (PLL/VCO)             | www.national.com/wireless    | PowerWise® Design<br>University | www.national.com/training      |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

#### Copyright© 2009 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959

National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com