## LDO Regulator Stability Using Ceramic Output Capacitors

## Introduction

Ultra-low ESR capacitors such as ceramics are highly desirable because they can support fast-changing load transients and also bypass very high frequency noise coming from switching converter power sources which a linear regulator can not reject. However, using ultra-low ESR capacitors on the output of an LDO regulator requires that specific design changes be implemented to ensure loop stability.

This article outlines the fundamentals of LDO loop compensation with respect to how the output capacitor's characteristics affect stability, also detailing the internal design techniques used to make LDO's which are stable when using ceramic output capacitors.

For more information on linear regulator compensation theory, refer to application note AN-1148: "Linear Regulators: Theory of Operation and Compensation".

## LDO Regulator Basic Operation

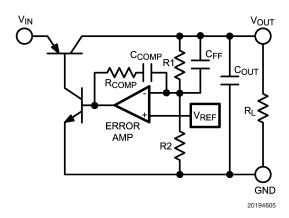

The LDO (low dropout) linear voltage regulator is unique because it can regulate the output voltage with an input voltage which may be within a few hundred millivolts of the output voltage. It can do this because the pass transistor is a single PNP (or P-FET) device, which can be driven fully into saturation. This means the dropout voltage (the minimum required voltage difference from input to output) is the lowest of any linear regulator type (see *Figure 1*).

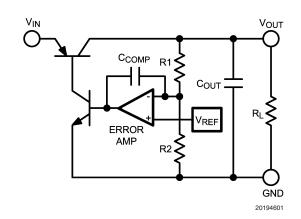

FIGURE 1. Typical PNP LDO Regulator

The LDO regulates it's output voltage by using an error amplifier to increase or decrease current drive to the PNP pass transistor as required by the load. Resistors R1 and R2 provide the voltage feedback from the output to the error amplifier, which compares this voltage to a fixed reference voltage. Negative feedback within the loop always forces the National Semiconductor Application Note 1482 Chester Simpson May 2006

voltages at both inputs of the error amplifier to be equal. The output voltage is set by the ratio of the two resistors:

$V_{OUT} = V_{REF} (1 + R1/R2)$

## LDO Loop Compensation

The P-type pass transistor of the LDO regulator drives the load off the collector (or drain), a configuration which has inherently high output impedance. Because of this, the capacitor connected to the output forms a pole with the load resistor whose frequency is given by:

$$P_{LOAD} = 1 / (2 X \pi X * R_{OUT} X C_{OUT})$$

$^{*}\text{R}_{\text{OUT}}$  is here defined as the effective impedance from the output node to ground: this is actually the parallel combination of:

- 1. the load resistance RL

- 2. the sum of R1 + R2

F

3. the output impedance of the pass transistor

However, in most cases, the load resistance is orders of magnitude less than the other two elements, so  $R_{OUT}$  can be approximated as  $R_L$ :

$$P_{LOAD} \simeq 1 / (2 X \pi X R_L X C_{OUT})$$

P<sub>LOAD</sub> will be designated the **Load Pole**.

The frequency of the load pole varies with load resistance. As an example, an LDO using a 10  $\mu$ F output capacitor driving a 3.3  $\Omega$  load has a load pole at:

$$P_{LOAD} \simeq 1 / (2 X \pi X 3.3 \Omega X 10 \mu F) = 4.8 \text{ kHz}$$

However, if the external load is disconnected (leaving only the regulator's internal resistive divider for a "load"), the frequency of the load pole may drop to less than one Hertz. This illustrates how the LDO load pole varies over a wide frequency range from "no load" to "full load" operation.

For this example, we will assume that the capacitor  $C_{COMP}$  will be used to add an "integrator" pole which is at a frequency of about 500 Hz. This means that the loop has two poles, which could potentially produce a phase shift of -180 degrees and cause oscillations. The methods used to add phase lead to offset the phase lag of the poles will be discussed in the following sections.

It should be noted that there are additional high-frequency poles, so care must be taken to ensure that the loop bandwidth does not get too wide, or they will add enough phase lag to create an oscillator. The power device contributes one such pole: for example, the input capacitance of the P-FET used as a pass device forms a pole with the output impedance of the circuitry driving it's gate. Because this highfrequency pole is associated with the power device, it will be referred to as the **Power Pole** ( $P_{PWR}$ ). For purposes of analysis, it will be assumed to be a fixed pole at a frequency located at about 500 kHz.

## Methods For Adding Phase Lead

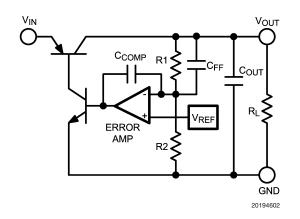

The poles in the loop of the LDO can cause oscillations if not compensated for by other zeroes which will add some phase lead. One of the traditional methods for doing that is to add a feedforward capacitor across resistor R1 (*Figure 2*), which forms a pole-zero pair. The zero is at a lower frequency than the pole, which allows placing the zero at a frequency before the unity gain crossover occurs. In this way, the zero adds a significant amount of lead, while the associated pole (which is at a higher frequency) adds only a small amount of additional lag. This results in a net gain of phase lead and improved phase margin.

#### FIGURE 2. LDO Regulator with Feed-Forward Compensation

The capacitor  $C_{\rm FF}$  forms a zero with R1 whose frequency is given by:

$$Z_{FF} = 1 / (2 \times \pi \times R1 \times C_{FF})$$

And  $C_{FF}$  forms a pole with the parallel combination of R1 and R2, whose frequency is given by:

#### $P_{FF} = 1 / (2 \times \pi \times R1 // R2 \times C_{FF})$

It's important to note that at higher output voltages (where R1 is much larger than R2), the pole and zero are far apart in frequency, allowing a much larger improvement in phase margin. At lower output voltages, the frequency of the pole and zero move closer together. The maximum possible phase lead provided by this method goes away quickly as the output voltage reduces, and it becomes completely useless when the output voltage equals the reference voltage. For this reason, relying on this compensation technique alone is adequate only for higher output voltages.

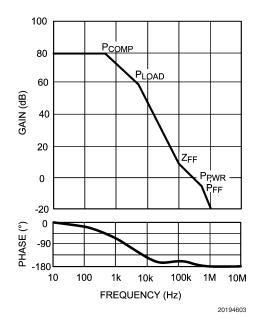

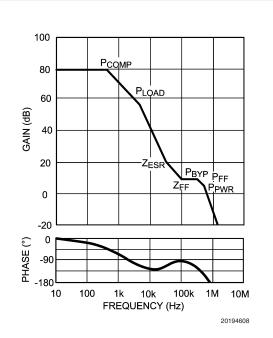

As an example, the gain and phase of a typical LDO will be calculated. Since LDO bandwidth is maximum at full load, that operating point will be used for the calculation. The following assumptions will be used:

1.25V reference, regulator set to 6.25V output.

$$\begin{split} & V_{OUT} / V_{REF} = 5 \\ & \text{Open loop gain} = 80 \text{ dB} \\ & P_{COMP} = 500 \text{ Hz} \\ & P_{LOAD} = 4.8 \text{ kHz} (C_{OUT} = 10 \text{ }\mu\text{F}, \text{ }R_L = 3.3 \text{ }\Omega\text{)} \\ & P_{PWR} = 500 \text{ kHz} \\ & \text{R1} = 40 \text{ }k\Omega \\ & \text{R2} = 10 \text{ }k\Omega \end{split}$$

Unity gain crossover frequency estimate = 300 kHz

The optimum frequency location for the feedforward zero is typically about 1/3 of the unity gain crossover frequency. Therefore, a zero frequency of 100 kHz will be assumed for the example, giving a C<sub>FF</sub> value of 39 pF. The pole formed by C<sub>FF</sub> and R1//R2 will be located at about 500 kHz, essentially forming a double pole with P<sub>PWB</sub> at 500 kHz.

Computing the phase for this set of component values and operating conditions shows a calculated phase margin of about 11 degrees at the unity gain crossover frequency of 300 kHz (see *Figure 3*). This is barely stable, certainly a very marginal design if no other compensation method was used.

#### FIGURE 3. Gain/Phase Plot for Typical LDO Using Only Feed-Forward Compensation

While feedforward compensation is used in most LDO's to obtain whatever positive phase shift it can generate, additional phase lead must usually be derived by other means to obtain an acceptable phase margin. The following section details the method used in the vast majority of LDO regulators: output capacitor ESR compensation.

# Output Capacitor ESR Compensation

Every capacitor contains some kind of parasitic resistance, which means a real capacitor can be modeled as a resistor in series with an ideal capacitor. This series resistance is typically referred to as **ESR** (equivalent series resistance).

The internal ESR forms a zero with the output capacitor whose frequency can be calculated from:

$$Z_{ESR} = 1 / (2 X \pi X ESR X C_{OUT})$$

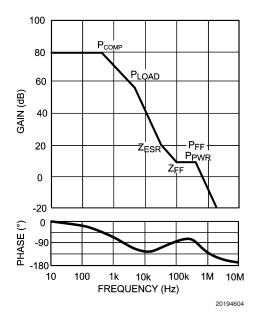

The frequency location of this zero for Tantalum capacitors is typically ideally positioned for LDO compensation: a typical 10  $\mu$ F Tantalum capacitor might have an ESR in the range of about 0.5 Ohm, giving a zero at a frequency of about 30 kHz. This zero will be added to the example previously developed and displayed in a gain/phase plot. *Figure 4* shows the additional phase margin derived from the addition of the ESR zero:

#### FIGURE 4. Gain/Phase Plot for Typical LDO Using Both Feed-Forward and ESR Compensation

The inclusion of the ESR zero into the example increased the calculated bandwidth from about 300 kHz to 600 kHz, but most important: it increased phase margin from 11 degrees up to about 68 degrees (which is extremely stable).

This example illustrates why most LDO's have a published "stable range" of ESR values which the output capacitor

must meet to ensure stable regulator operation: the ESR zero is the dominant compensation element for the loop. The "maximum" value boundary for ESR sets the lower limit for the zero frequency, which must not be so low that it increases loop bandwidth to the point that high frequency poles cause instability. The "minimum" ESR value boundary sets the maximum frequency for the zero, which must not be so high that it occurs so far after the unity-gain crossover frequency that it can no longer add enough phase lead to get sufficient phase margin for stable operation.

## Ceramic Capacitors: ESR = milliohms

Ceramic capacitors do contain some parasitic ESR, but for capacitance values greater than 1 uF, the value of ESR is usually in the range of a few milliohms at high frequencies. This makes ceramic capacitors extremely attractive for bypassing high frequency noise and supporting rapidly changing load transients, but it also makes them unsuitable for use with LDO's which were designed to rely on the output capacitor's ESR for the loop compensation zero. A 10  $\mu$ F capacitor whose ESR is in the 5 milliohm range is providing a zero at a frequency above 3 MHz. As illustrated in the previous example, that frequency is too high to add enough phase lead to provide adequate phase margin at the unitygain frequency.

LDO's which are stable with ultra-low ESR output capacitors have a zero built into the error amplifier compensation network. Instead of a simple integrator using only a single feedback capacitor  $C_{\rm COMP}$ , a resistor is added in series (*Figure 5*). This combination of feedback elements creates both the integrator pole as well as a zero. This resistor (shown as  $R_{\rm COMP}$ ), provides a zero which performs the same function as the ESR zero, and will allow the use of ceramic output capacitors while maintaining good phase margin.

This design technique lowers the "minimum stable ESR" limit down to essentially zero Ohms, but it also lowers the maximum stable ESR limit as well. To understand why, it should be noted that since the error amplifier provides a zero inside the loop bandwidth, adding another zero will increase the bandwidth too much and allow high frequency poles to create instability.

A typical LDO designed to work with electrolytic output capacitors may have a stable ESR range of about 0.1 Ohm up to 10 Ohms. The "ceramic stable" version with an internal zero added allows ESR values down to zero Ohms, but the upper limit may be as low as about 0.5 Ohm (depending on load current and size of  $C_{OUT}$ ).

AN-1482

AN-1482

## Ceramic Capacitors: ESR = milliohms (Continued)

#### FIGURE 5. Ceramic-Stable LDO with Internal Compensation Zero

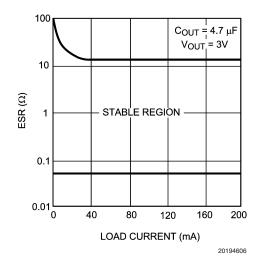

An example of the stable ESR range of a typical "electrolytic stable" LDO is shown in *Figure 6*. This is a reproduction of the ESR curve shown in the LP2988 data sheet. The data points used to generate such ESR curves are empirically derived from bench testing by using a ceramic output capacitor (which has essentially no ESR) and soldering in discrete resistance values in series with it to find the point of instability at various load currents, with data being taken at both temperature extremes.

FIGURE 6. C<sub>OUT</sub> ESR Stability Boundaries for Typical "Electrolytic Stable" LDO

As show, the lower limit of stable operation is approximately 50 milliOhms, which is too high to allow the use of ceramic output capacitors, unless some external resistance is added in series with them. The upper ESR limit (which sets the lower frequency of the ESR zero) shows a ramp up at very light loads. This is due to the fact that the load pole moves to a lower frequency at very light loads (reducing loop bandwidth), allowing the frequency of the ESR zero to go lower and still have stable operation.

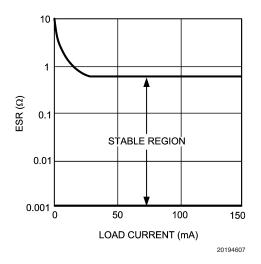

The ESR curve for a "ceramic stable" LDO regulator is shown in *Figure 7*. The lower limit of stable ESR is zero Ohms, and the upper limit is about 0.5 Ohms except at very light load currents where the upper limit rises. As before, the reason the limit rises there is that the load pole drops to a very low frequency at light loads making the loop stable with the compensation zero at a lower frequency.

#### FIGURE 7. C<sub>OUT</sub> ESR Stability Boundaries for Typical "Ceramic Stable" LDO

Based on these curves, it can be seen that the use of ceramic output capacitors is generally reserved for parts which are designed to use them. However, the "ceramic stable" LDO does have enough headroom on the upper ESR limit that low-ESR Tantalum and aluminum electrolytics may be used.

## Additional Poles From Ceramic "Bypass" Capacitors

In many designs, especially ones where digital IC's are present, bypass capacitors are often sprinkled throughout the PC board at the  $V_{\rm CC}$  pin of every device powered by the voltage regulator. In most cases, these are small ceramic capacitors whose value is in the .01  $\mu$ F to 0.1  $\mu$ F range. These capacitors can cause LDO regulators to oscillate, and the reason is often not understood by the user.

As previously explained, a capacitor connected to the output of an LDO forms a "load pole" in conjunction with the effective resistance from the output node to ground:

$P_{LOAD} = 1 / (2 X \pi X R_{OUT} X C_{OUT})$

What may not be obvious is that small capacitors connected to the output can add an unwanted pole at a frequency which can reduce or eliminate phase margin. LDO regulators which use electrolytic output capacitors (and rely on their ESR for the compensation zero) are vulnerable to this effect.

The previously derived example (gain/phase plots are shown in *Figure 4*) will be used to explain how this can occur:

Open loop gain = 80 dB

$$\begin{split} & V_{OUT} \ / \ V_{REF} = 5 \\ & P_{COMP} = 500 \ Hz \\ & P_{LOAD} = 4.8 \ \text{kHz} \ (C_{OUT} = 10 \ \mu\text{F}, \ \text{R}_{L} = 3.3 \ \Omega) \\ & P_{PWR} = 500 \ \text{kHz} \\ & \text{R1} = 40 \ \text{k}\Omega \\ & \text{R2} = 10 \ \text{k}\Omega \\ & \text{R2} = 10 \ \text{k}\Omega \\ & C_{FF} = 39 \ \text{pF} \ (P_{FF} = 510 \ \text{kHz}, \ Z_{FF} = 100 \ \text{kHz}) \\ & C_{OUT} = 10 \ \mu\text{F} \ \text{Tantalum} \ / \ \text{ESR} = 0.5\Omega \end{split}$$

(ESR zero frequency = 30 kHz)

Unity gain crossover frequency estimate  $\approx$  600 kHz

Phase margin = 68 degrees (without ceramic output capacitance added)

The previously calculated phase margin is about 68 degrees (very stable) with only a 10  $\mu$ F Tantalum output capacitor. What happens if a total of ten 0.1  $\mu$ F ceramic "bypass" capacitors are connected to the output of the LDO, effectively creating a 1  $\mu$ F ceramic capacitor in parallel with the 10  $\mu$ F Tantalum?

To calculate the new pole created by the ceramic bypass capacitors:

$$P_{LOAD} = 1 / (2 X \pi X R_{OUT} X C_{OUT})$$

In calculating R<sub>OUT</sub>, we are most concerned with the impedance from output to ground at frequencies near the unitygain crossover (about 600 kHz). In that frequency range, the 10 µF Tantalum capacitor would effectively look like a 0.5Ω resistor from output to ground, the 3Ω load resistor would be in parallel with it, yielding an effective value for R<sub>OUT</sub> of about 0.43Ω. The pole resulting from this impedance and the ceramic capacitors is:

$P_{BYP} = 1 / (2 X \pi X 0.43 X 1 \mu F) = 370 \text{ kHz}$

Assuming the unity-gain frequency is still approximately 600 kHz, this added pole would drop the phase margin from 68 degrees down to about 9 degrees (very poor). This gain/ phase plot is shown in *Figure 8*.

### FIGURE 8. Phase Margin Reduced by 1 µF Ceramic Capacitor Connected to the Output

This example illustrates how even a relatively small amount of ceramic capacitance added to the output of an LDO not designed for ceramics can cause it to go unstable. The incorrect assumption typically made is that when a small capacitor is in parallel with a larger capacitor, the smaller one's effect will be "swamped out" by the larger one. However, the smaller value of capacitance made up by the "bypass capacitors" will form it's own pole. If that pole is near or below the unity-gain crossover frequency of the loop, it can add enough phase lag to create an oscillator.

## Minimizing Effect of Bypass Capacitors

Since small value ceramic capacitors placed on the output of LDO regulators can reduce phase margin, care should be taken to keep these as far as possible from the output terminal of the regulator. Capacitors whose value is in the range of about .01  $\mu F$  to 0.1  $\mu F$  are usually the most problematic.

Trace inductance in series with these capacitors will help decouple their resonant effect. Since board layouts vary, a "safe distance" boundary for all applications can not be given. Narrow copper traces have significantly higher inductance than copper planes, so the "affecting distance" of the capacitors increases when power planes and ground planes are used to route power across the board.

The reliable way to determine if board capacitance is reducing phase margin is to perform load step testing on the actual board with all capacitors in place. The IC's which the regulator powers should be removed (or not installed) and a resistor should be used at the output of the regulator which provides the same load current. The load should be stepped from no load to rated load while the output is watched for ringing or overshoot during the load step transient: excessive ringing indicates low phase margin.

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### BANNED SUBSTANCE COMPLIANCE

National Semiconductor follows the provisions of the Product Stewardship Guide for Customers (CSP-9-111C2) and Banned Substances and Materials of Interest Specification (CSP-9-111S2) for regulatory environmental compliance. Details may be found at: www.national.com/quality/green.

Lead free products are RoHS compliant.

National Semiconductor Americas Customer Support Center Email: new.feedback@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +44 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790 National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560

www.national.com

AN-1482