# AN-1560

## LP38852MR-ADJ Evaluation Board

National Semiconductor Application Note 1560 Don Jones December 2006

### Introduction

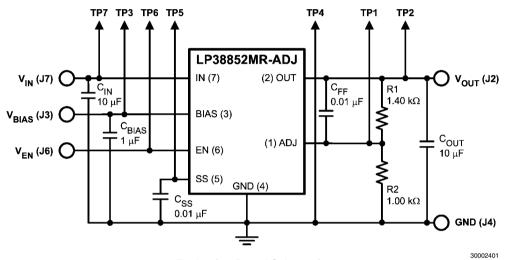

This board is designed to allow the evaluation of the LP38852MR-ADJ Voltage Regulator. Each board is assembled and tested in the factory. This evaluation board has the PSOP-8 package mounted, and the output voltage is set to 1.20V.

### **General Description**

The LP38852 is a dual-rail adjustable LDO linear regulator capable of suppling up to 1.5A of output current, and incorporates an Enable function as well as a Soft-Start function.

The device has been designed to work with 10  $\mu$ F input and output ceramic capacitors, and 1 $\mu$ F bias capacitor. Footprints areas for C<sub>IN</sub> and C<sub>OUT</sub> will allow for a variety of sizes.

### **Operation**

The input voltage, applied between  $V_{\rm IN}$  and GND, should be at least 1.0V greater than  $V_{\rm OUT}$  and no greater than the applied  $V_{\rm RIAS}$  voltage.

The bias voltage, applied between  $V_{\rm BIAS}$  and GND should be above the minimum bias voltage of 3.0V, and no more than the maximum of 5.5V.

Loads can be connected to  $V_{\rm OUT}$  with reference to GND.

${

m V_{OUT}}$  and  ${

m V_{IN}}$  test points are provided on the board to allow accurate measurements directly onto the input and output pins of the device, eliminating any voltage drop on the PCB traces or connecting wires to the load.

### **Setting Vout**

The output voltage is set using the external resistive divider R1 and R2. The output voltage is given by the formula:

$$V_{OUT} = V_{ADJ} x (1 + (R1 / R2))$$

(1)

It is recommended that the values selected for R1 and R2 are such that the parallel value is less than 10 k $\Omega$ . This is to prevent internal parasitic capacitances on the ADJ pin from interfering with the F $_{Z}$  pole set by R1 and C $_{FF}$ .

The LP38852MR-ADJ Evaluation board is assembled with a 1.40 k $\Omega$  ±1% resistor for R1, and a 1.00 k $\Omega$  ±1% resistor for R2. This sets V<sub>OUT</sub> to 1.20V.

### Selecting C<sub>FF</sub>

A capacitor placed across the gain resistor R1 will provide additional phase margin to improve load transient response of the device. This capacitor,  $C_{\text{FF}}$ , in parallel with R1, will form a zero in the loop response given by the formula:

$$F_Z = (1 / (2 \times \pi \times C_{FF} \times R1))$$

(2)

The value for  $C_{FF}$  should be selected to set a zero frequency  $(F_7)$  between 10 kHz and 15 kHz using the formula:

$C_{EE} = 1 / (2 \times \pi \times F_7 \times R1)$  (3)

The closest standard 10% value is usually adequate for  $C_{FF}$ . The LP38853-ADJ Evaluation board is assembled with a 0.01  $\mu$ F capacitor for  $C_{FF}$ . This sets  $F_7$  to approximately 11.4 kHz.

30002407

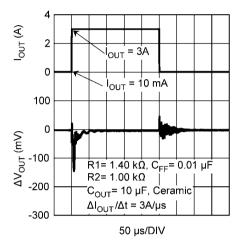

FIGURE 1. 10mA to 3A Load Transient Response

30002408

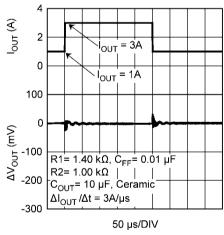

FIGURE 2. 1A to 3A Load Transient Response

### **Enable Function**

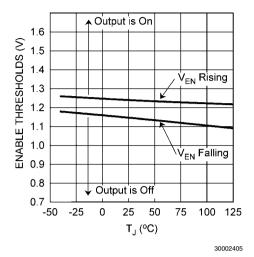

ON/OFF control is provided by supplying a logic level signal to the Enable pin. A minimum  $V_{EN}$  value of 1.3V is typically required at this pin to enable the LDO output. The LDO output will be shutdown when the  $V_{EN}$  value is typically 1.0V or less. The  $V_{EN}$  threshold incorporates approximately 100mV of hysteresis.

In applications were the LP38852 is operated continuously the Enable pin can be connected directly to  $V_{\text{BIAS}}$ , or left open.

The Enable pin has a 200 k $\Omega$  internal resistor to  $V_{BIAS}$ . If the Enable pin is left open, care should be taken to minimize any capacitance on the Enable pin, as any capacitance will introduce an RC delay time on the Enable function.

FIGURE 3. Enable Thresholds

### **Soft-Start Function**

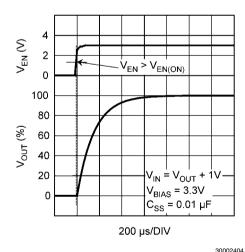

$V_{\rm REF}$  will rise at an RC rate defined by the internal resistance of the SS pin  $(r_{\rm SS})$ , and the external capacitor  $(C_{\rm SS})$  connected to the SS pin. This allows the output voltage to rise in a controlled manner until steady-state regulation is achieved. Typically, five time constants are recommended to assure that the output voltage is sufficiently close to the final steady-state value. During the soft-start time the output current can rise to the built-in current limit.

The LP38852MR-ADJ Evaluation board is assembled with a 0.01  $\mu$ F capacitor for C<sub>SS</sub>. This sets the soft-start time to approximately 750  $\mu$ s.

FIGURE 4. V<sub>OUT</sub> Soft-Start

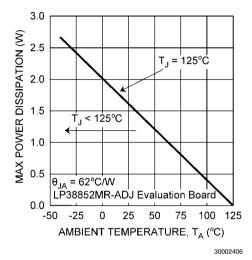

### **Power Dissipation**

The LP38852MR PSOP-8 package alone has a junction to ambient thermal resistance ( $\theta_{JA}$ ) rating of 168°C/W. When mounted on the LP38852MR evaluation board the  $\theta_{JA}$  rating is approximately 62°C/W.

Although there is only approximately 0.03 square inches (0.1 x 0.3) 1 ounce copper area immediately under the DAP, the top copper surface area is extended to additional copper area on the bottom of the board by four thermal vias.

With the 62°C/W thermal rating the LP38852MR-ADJ evaluation board will dissipate a maximum of 1.6W with  $T_A = 25$ °C.

FIGURE 5. Maximum Power Dissipation vs Ambient Temperature

www.national.com

2

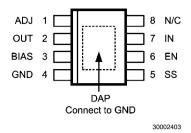

### **Connection Diagram**

### **Schematic Diagram**

**Evaluation Board Schematic.**

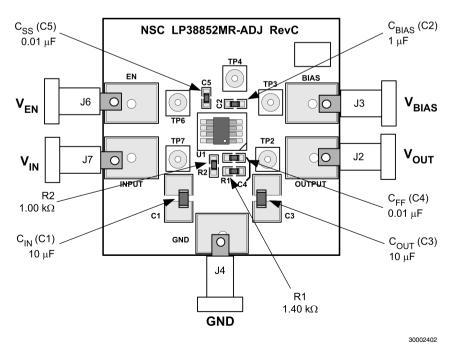

### **PCB Layout**

**Evaluation Board Component and Pin Layout**

3

www.national.com

### **Bill of Materials**

| ID  | Name               | Description                                                   | Manufacturer                          | Part Number        |

|-----|--------------------|---------------------------------------------------------------|---------------------------------------|--------------------|

| U1  | U1                 | LP38852MR-ADJ NOPB                                            | National Semiconductor<br>Corporation | LP38852MR-ADJ NOPB |

| C1  | C <sub>IN</sub>    | Capacitor: 10 μF; ±10%; MLCC; 10V;<br>X7R; 1210               |                                       | 1210ZC106KAT2A     |

| C2  | C <sub>BIAS</sub>  | Capacitor: 1 μF;, ±10%; MLCC; 10V;<br>X7R; 0805               |                                       | 0805ZC105KAT2A     |

| СЗ  | C <sub>OUT</sub>   | Capacitor: 10 μF;, ±10%; MLCC; 10V; X7R; 1210                 | AVX                                   | 1210ZC106KAT2A     |

| C4  | C <sub>FF</sub>    | Capacitor: 0.01 μF;, ±10%; MLCC; 10V; X7R; 0805               |                                       | 0805YC103KAT2A     |

| C5  | C <sub>ss</sub>    | Capacitor: 0.01 μF; ±10%;, MLCC; 10V; X7R; 0805               |                                       | 0805YC103KAT2A     |

| J2  | V <sub>EN</sub>    | Banana Jack : Insulated Solder<br>Terminal; White             |                                       | 108-0901-001       |

| J3  | V <sub>IN</sub>    | Banana Jack : Insulated Solder<br>Terminal; Red               | Johnson Components                    | 108-0902-001       |

| J4  | GND                | Banana Jack : Insulated Solder<br>Terminal; Black             |                                       | 108-0903-001       |

| J6  | V <sub>OUT</sub>   | Banana Jack : Insulated Solder<br>Terminal; Orange            |                                       | 108-0906-001       |

| J7  | V <sub>BIAS</sub>  | Banana Jack : Insulated Solder<br>Terminal; Blue              |                                       | 108-0910-001       |

| R1  | R1                 | Resistor: 1.40 kΩ, ±1%; Thick Film;<br>250 mW; ±100 ppm; 0805 | VISHAY DALE                           | CRCW 0805 1401 F   |

| R2  | R2                 | Resistor: 1.00 kΩ, ±1%; Thick Film; 250 mW; ±100 ppm; 0805    |                                       | CRCW 0805 1001 F   |

| TP2 | TP <sub>EN</sub>   | Turret Terminal : Mounting Hole Diameter = 0.062"             | Keystone                              | 1593–2             |

| TP2 | TP <sub>SS</sub>   |                                                               |                                       |                    |

| TP3 | TP <sub>IN</sub>   |                                                               |                                       |                    |

| TP4 | TP <sub>GND</sub>  |                                                               |                                       |                    |

| TP5 | TP <sub>ADJ</sub>  |                                                               |                                       |                    |

| TP6 | TP <sub>OUT</sub>  |                                                               |                                       |                    |

| TP7 | TP <sub>BIAS</sub> |                                                               |                                       |                    |

www.national.com

# Notes 5

### **Notes**

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2007 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Customer Support Center Email: new.feedback@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Customer Support Center Fax: 449 (0) 180-530-85-86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +49 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790 National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560