# **Design and Layout Guidelines for SCAN25100**

National Semiconductor AN-1463 Lee Sledjeski October 21, 2009

# **Description**

The SCAN25100 is a 2457.6, 1228.8, and 614.4 Mbps serializer/deseralizer (SerDes) for high-speed bidirectional serial data transmission over FR-4 printed circuit board backplanes. balanced cables, and optical fiber. This high-speed operation is achieved without significant layout and overall PCB design constraints. However, adhering to a few specific layout guidelines will optimize signal integrity and performance.

- AC coupling capacitor placement, size and value.

- High speed differential signaling options (microstrip / stripline / twin-ax cable)

- **REFCLK** terminations

- 4. DDR impedance recommendations

- 5. Decoupling

- 6. Power Filtering

- Thermal recommendations

# AC Coupling On DOUT and RIN

In many cases the SCAN25100 will be interfacing to a SFP (Small Form Factor Pluggable) or similar Optical Transceiver. This type of connection is always AC coupled, many optical modules available today already include AC coupling. This means the PCB connection between the SCAN25100 and the optical module will be a direct interconnect and will not require any additional passive components.

In applications that involve copper cables, the transmission distance will be limited by the loss characteristics of the cable. The ability of the SCAN25100 CML IO to use de-emphasis and equalization will extend the transmission distance beyond 20 meters in most cases. For when cables are used between sub-systems that reside 10's of meters apart, significant ground shifts often occur. To combat this issue, external AC coupling capacitors must be inserted in the signal path. Though the placement of these DC blocking capacitors is not critical, choosing the correct value and minimum body size will minimize any impedance discontinuities in the signal path.

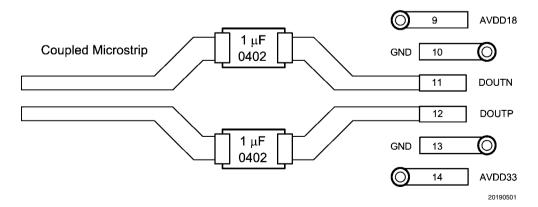

The most common serial encoding used with the SCAN25100 will be 8B/10B. This scheme limits the maximum run length of consecutive 0's or 1's to 5 bits, thereby defining our minimum frequency of interest when selecting an AC coupling capacitor value. For the SCAN25100 a capacitor value of 1.0 μF will give excellent signal fidelity at all CPRI rates. A smaller capacitor may be chosen if only the fastest rate of 2.4576 Gbps will be used in the application. For the physical size smaller is better, microstrip lines that support 50 ohm singleended or 100 ohm differential impedance will always be less then 20 mils wide and in some differential cases, much less. Keeping the body width of the AC coupling capacitor nearly the same size as the microstrip line width minimizes signal losses and impedance discontinuities. A picture showing AC coupling capacitors is shown in Figure 1.

FIGURE 1. AC Coupling on the SCAN25100 CML IO

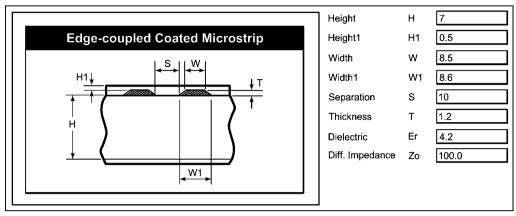

Component to component spacing constraints will not allow running differential lines to the capacitors. As the spacing between the lines is increased the coupling is reduced and the PCB traces begin to act as single-ended traces instead of differential traces. To compensate for this the width of the PCB traces will have to be enlarged to maintain a constant impedance profile. An example  $100\Omega$  differential microstrip is

shown in *Figure 2*. To maintain the impedance at  $100\Omega$  when the traces are uncoupled (S >> W), the width must be increased by 3.4 mils to 12 mils.

If the PCB trace width in *Figure 1* had not been increased, a short segment of 115 $\Omega$  transmission line would be seen in the signal path resulting in increased jitter.

20190502

FIGURE 2. Edge-Coupled Microstrip Line with  $100\Omega$  Impedance

# **High Speed Signaling Options**

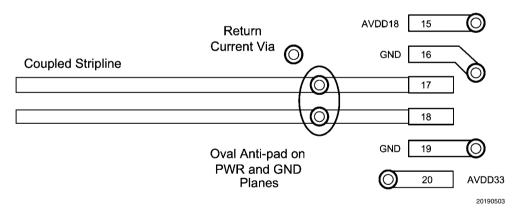

In many cases the SCAN25100 will be interfacing to a SFP (Small Form Factor Pluggable) or similar Optical Transceiver. This type of connection is likely to be very short. Due to the relatively short length it is possible to route the signals on the top layer as differential microstrip. When longer connections are required it is preferable to utilize internal signal layers to

minimize the opportunity to pick up interference from other noise sources. Using internal PCB layers for high speed signaling will also minimize emissions from the high-speed CML signals. Vias are used to move between PCB layers, an example of this is shown in *Figure 3*.

FIGURE 3. Differential Vias with Oval Anti-pad

Small vias, with a drill size of 8 mils or less, should be used to minimize mutual capacitive coupling between via and nearby ground or power planes. Differential via structure with shared oval-shaped anti-pad can further reduce parasitic capacitance. Placing a return current via immediately adjacent

to the signal vias will improve signal fidelity at multi-gigabit speeds. The return current via allows a low inductance path between reference planes in the PCB minimizing the impedance discontinuity across the via structure.

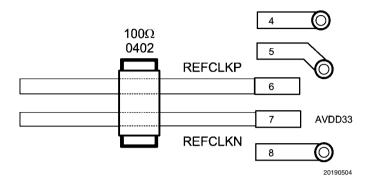

### **REFCLK Termination**

There are several possibilities for input termination on REF-CLKP/N. The most common termination, especially for LVDS outputs like SYSCLK will be a simple  $100\Omega$  resistor across the differential input. This resistor should be placed the minimum distance from the REFCLK inputs as shown in *Figure*

For LVPECL style outputs the termination requirements may vary. The termination style can generally be determined from the manufacturers datasheet. Most common is a  $2x50\Omega$  center tapped termination to  $V_{DD}-2.1\ volts.$

FIGURE 4. 100Ω Termination on REFCLK Inputs

## **DDR Impedance Recommendations**

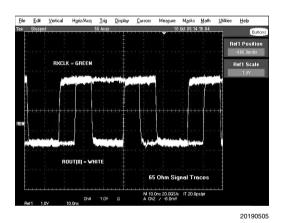

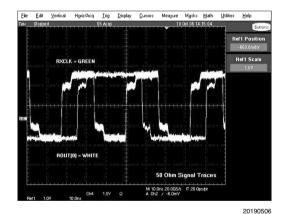

The SCAN25100 has been designed with DDR outputs intended to drive transmission lines with a nominal impedance of  $60-65\Omega$ . The outputs ROUT[0:9] and RXCLK rely on reflected wave switching for good signal integrity and low dynamic power. For this interface no internal or external

termination is required at the load. The only requirement is for the PCB layout to be designed to achieve a nominal impedance of  $60\Omega\text{--}65\Omega.$  This matches the nominal output impedance of the DDR outputs.

FIGURE 5.  $65\Omega$  Environment on Left and  $50\Omega$  Environment on Right.

3

As shown in Figure 5, choosing a PCB impedance lower then  $60\Omega$  will result in reduced noise margins, PCB impedance

## **Decoupling**

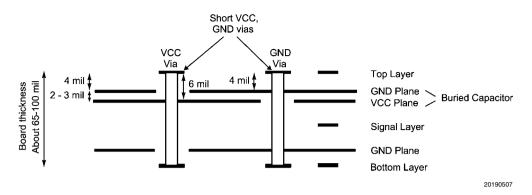

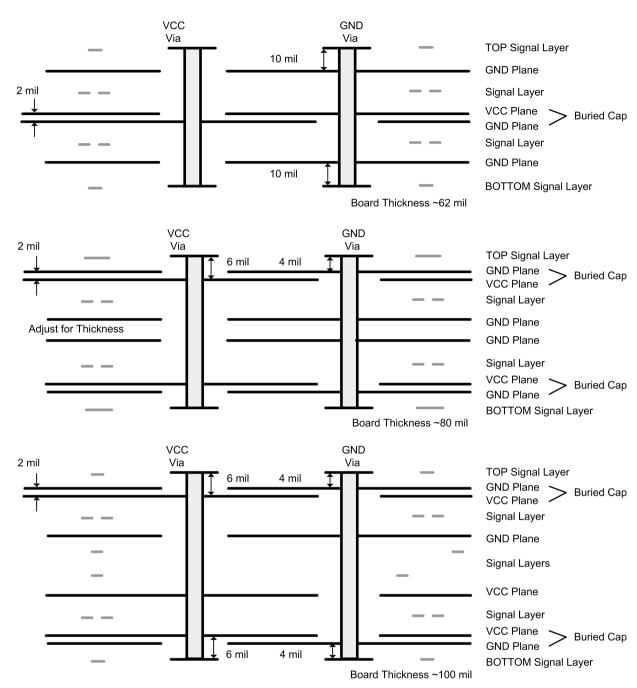

Each power or ground lead of the SCAN25100 should be connected to the PCB through a low inductance path. For best results, one or more vias are used to connect a power or

above  $65\Omega$  will result in some overshoot and undershoot noise at the load.

ground pin to the nearby plane. Ideally, via placement is immediately adjacent to the pin to avoid adding trace inductance. Placing power plane closer to the top of the board reduces effective via length and its associated inductance.

FIGURE 6. Low Inductance, High Capacitance Power Connection

Bypass capacitors should be placed close to VDD pins. They can be conveniently placed near the corners of the TQFP package. Small physical size capacitors, such as 0402, X7R, surface mount capacitors should be used to minimize body inductance of capacitors. Each bypass capacitor is connected to the power and ground plane through vias tangent to the pads of the capacitor. An X7R surface mount capacitor of size 0402 has about 0.5 nH of body inductance. At frequencies above 30 MHz or so, X7R capacitors behave as low impedance inductors. To extend the operating frequency range to a few hundred MHz, an array of different capacitor

values like 100 pF, 1 nF, 0.03  $\mu$ F, and 0.1  $\mu$ F are commonly used in parallel. The most effective bypass capacitor can be built using sandwiched layers of power and ground at a separation of 2–3 mils. With a 2 mil FR4 dielectric, there is approximately 500 pF per square inch of PCB. An example of this is shown in *Figure 6*.

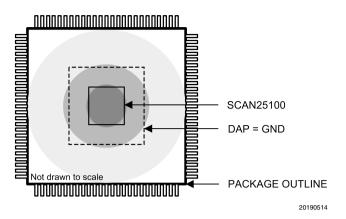

The center dap of the TQFP package housing the SCAN25100 should be connected to a ground plane through an array of vias. The via array reduces the effective inductance to ground and enhances the thermal performance of the TQFP package.

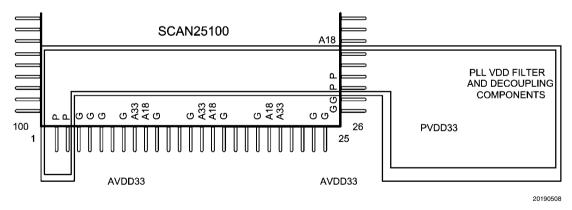

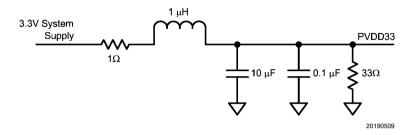

### **Power Filtering**

The PVDD33 supply is used to provide power to the onboard PLL and CDR units. Keeping this supply free of noise ensures optimal device performance. Isolating the PLL supply from the other SCAN25100 supply connections and more importantly large sources of digital noise like FPGAs is the easiest way to keep noise low. *Figure 7* shows an island VDD connection for the PLL and CDR supply pins. Input power to this island is routed through either an LC low pass filter. Local decoupling for the PLL and CDR supply connections must also be pro-

vided on-board to further filter and stabilize this supply voltage. While creating this filtered power island it is important to consider the effects on other supply pins and return currents on the PCB. Reducing the size of the island to the area under the SCAN25100 eases PCB constraints, specific implementations should be checked to ensure no other supply issues have been created due to this area of isolation under the SCAN25100.

FIGURE 7. Isolated 3.3V Supply for PVDD33 Connections on the SCAN25100

The PVDD33 supply LC filter components should be chosen to provide significant attenuation at and above power supply switching frequencies in the system. Generally switching power supply frequencies have been increasing to reduce component size and cost. This trend in switching power supply design aids component selection for the SCAN25100 power supply filter. The external LC filter is a relatively simple

2nd order low pass design. Although the RC network is slightly cheaper, the solution limits the maximum attenuation that can be achieved.

The series R of an RC filter reduces the voltage on the PVDD33 pins. This constraint limits the value of resistance to relatively low values. Requiring a physically

- larger capacitor to achieve reasonable attenuation characteristics.

- With only one reactive element, the RC filter is a 1st order design. This limits attenuation to 20 dB/decade at higher frequencies.

To design an effective LC network it is best to start by defining the source and load impedances that are expected in the application. The PVDD33 has a typical current consumption of 80 mA with an absolute maximum of almost 100 mA. With a nominal supply voltage of 3.3V, the worst-case current consumption is equivalent to a 33 $\Omega$  load on our LC network. Since the input to our LC network is a power supply, the source impedance is certainly very low. Using  $1\Omega$  for the source impedance is a good approximation.

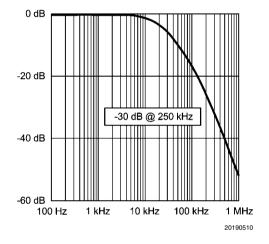

The design goal for this filter network was chosen to be -30 dB at a typical switching power supply frequency of 250 KHz. The response curve is shown in the graph below.

Due to the variables in any system design, no single LC filter can be considered optimal. The values selected in this example would likely exceed the filter requirements in most applications. An analysis for specific applications should be taken to ensure this SCAN25100 supply remains noise free.

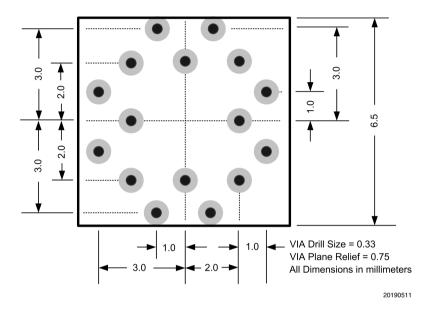

### **Thermal Recommendations**

The exposed GND pad on the TQFP-100 must be connected to GND using a copper land and multiple vias to ensure optimal thermal performance. Thermal vias connect the copper land to internal or external copper planes and should have a drill diameter sufficiently small so that the hole is effectively plugged when the barrel of the via is plated with copper. This plug is needed to prevent wicking the solder away from the interface between the package body and the thermal land on the surface of the board during solder reflow. Generally, a drill diameter of 0.33mm (13 mils) or smaller keeps solder wicking to a minimum.

To assure the optimum thermal transfer through the GND vias to internal planes or the reverse side of the PCB, the vias used in the thermal land should not be thermally relieved. Thermal relief or "Web" construction on PCB vias is a standard technique used in most PCBs today to facilitate soldering, by constructing the via so that it has a high thermal resistance. This is not desirable for heat removal from the TQFP-100 exposed GND package. It is recommended that all vias used under the package make internal connections to the planes using a continuous connection completely around the hole diameter for optimal thermal performance.

FIGURE 8. GND Via Placement for Optimal Heat Transfer

In many system designs airflow is routed across heat sinks attached to the bottom of the PCB. In cases like this, an external GND pad on the backside of the board will be needed to achieve the most efficient heat transfer. This pad should be at least as big as the DAP package connection. The board stackup will also effect how efficiently heat can be transferred from the TQFP-100 package.

Keeping the distance from the TOP and/or BOTTOM of the board to the GND plane is essential to good thermal conductivity. This minimizes the effective length and thermal resistance of the GND vias, maximizing the heat transfer to the PCB. In some cases two SCAN25100 devices will be mounted back to back to save PCB space. In this type of layout it is important that the PCB stackup has at least 2 GND planes so each SCAN25100 has its own primary GND plane for thermal dissipation. With only a single GND plane, package thermal performance will be impacted due to the combined power dissipation of two SCAN25100 devices connected to a common heat sink.

20190512

In this type of layout it is important that the PCB stackup has at least 2 GND planes so each SCAN25100 has its own primary GND plane for thermal dissipation. With only a single GND plane, package thermal performance will be impacted due to the combined power dissipation of two SCAN25100 devices connected to a common heat sink.

In all PCB stack-up designs shown there is at least one VCC-GND pair specified with the minimum manufacturing dielectric

thickness. At the minimum spacing the planes create a very low inductance parallel plate capacitor for high frequency decoupling.

The SCAN25100 device is centered above the 6.5 mm DAP connection inside the TQFP-100 package. Therefore heat from the SCAN25100 will also be centered within the DAP area.

FIGURE 9. TQFP-100 Temperature Profile

It is not recommended to add more then 16 vias under the DAP area. Increasing the via count further will not significantly improve the SCAN25100 thermal performance. The vias must also cut through the power planes. Too many local via

reliefs in the power plane will reduce the plane-to-plane decoupling capacitance and increase plane inductance in this critical supply area under the SCAN25100 component.

# Notes

## **Notes**

For more National Semiconductor product information and proven design tools, visit the following Web sites at:

| Products                       |                              | Design Support                  |                                |

|--------------------------------|------------------------------|---------------------------------|--------------------------------|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH® Tools                  | www.national.com/webench       |

| Audio                          | www.national.com/audio       | App Notes                       | www.national.com/appnotes      |

| Clock and Timing               | www.national.com/timing      | Reference Designs               | www.national.com/refdesigns    |

| Data Converters                | www.national.com/adc         | Samples                         | www.national.com/samples       |

| Interface                      | www.national.com/interface   | Eval Boards                     | www.national.com/evalboards    |

| LVDS                           | www.national.com/lvds        | Packaging                       | www.national.com/packaging     |

| Power Management               | www.national.com/power       | Green Compliance                | www.national.com/quality/green |

| Switching Regulators           | www.national.com/switchers   | Distributors                    | www.national.com/contacts      |

| LDOs                           | www.national.com/ldo         | Quality and Reliability         | www.national.com/quality       |

| LED Lighting                   | www.national.com/led         | Feedback/Support                | www.national.com/feedback      |

| Voltage Reference              | www.national.com/vref        | Design Made Easy                | www.national.com/easy          |

| PowerWise® Solutions           | www.national.com/powerwise   | Solutions                       | www.national.com/solutions     |

| Serial Digital Interface (SDI) | www.national.com/sdi         | Mil/Aero                        | www.national.com/milaero       |

| Temperature Sensors            | www.national.com/tempsensors | SolarMagic™                     | www.national.com/solarmagic    |

| Wireless (PLL/VCO)             | www.national.com/wireless    | PowerWise® Design<br>University | www.national.com/training      |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2009 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com

National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com