# Extending the Reach of a FPD-Link II Interface with Cable Drivers and Equalizers

National Semiconductor Application Note 1826 Davor Glisic, John Goldie March 24, 2008

National's family of embedded clock LVDS SER/DES (FPD-link II) provides a 2-wire serial interface for Display applications up to distances of 10 meters.

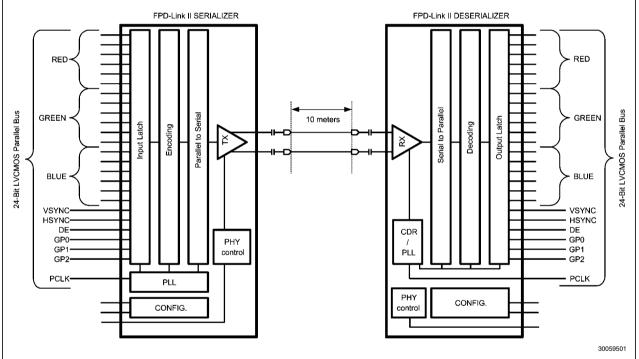

In the application example illustrated in *Figure 1*, the DS90UR241 is the SER device. It serializes the 18-bit RGB color information along with the three video control signals (VS, HS, and DE) and up to three additional General Purpose (GP0, GP1, and GP2) signals into a single high-speed FPD-Link II serial stream. The Display in the example is a Dual VGA (1280 x 480) resolution. At 60 fps and 10% blanking, the required PCLK is 40.5 MHz. Thus the serial rate is 28 times the PCLK or 1.134 Gbps. For applications up to 10 meters, the companion DES device, the DS90UR124, may be used.

It performs the Clock and Data Recovery (CDR) function and recreates the wide parallel bus.

In some applications, longer cables may be required that are beyond the capability of the integrated FPD-Link II Line Drivers and Receivers. Instead of using repeaters which would require circuitry and power in the middle of the link, a long haul cable driver / equalizer pair may be used to extend the reach of the cable to 100s of meters. In addition, a repeater would normally be able to restore only the signal amplitude but would not be able to reduce jitter induced by cable losses and inter-symbol interference; therefore, a repeater approach would provide a rather limited extension to a SER/DES link.

FIGURE 1. FPD-Link II SER/DES Application Example (10 meters or less)

# Cable Extender Chipset Enables Long Reach Applications for SER/DES

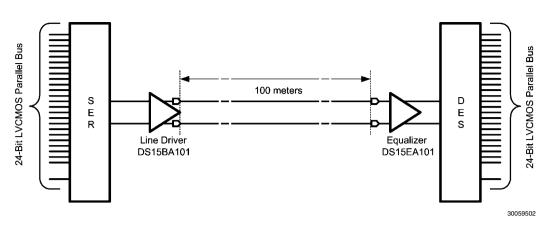

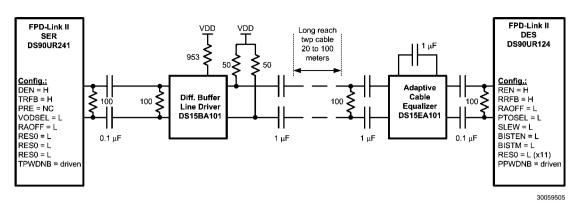

The DS15BA101 and DS15EA101 can be used as a Cable Extender chipset to enable long reach applications for

FPD-Link II SER/DES Display Links as shown in *Figure 2*. The length of the cable can now be greatly extended to more than 100 meters depending upon the serial transmission rate and also the cable characteristics.

FIGURE 2. Long Reach FPD-Link II SER/DES Application (100 meters or more)

### **Cable Extender Chipset Overview**

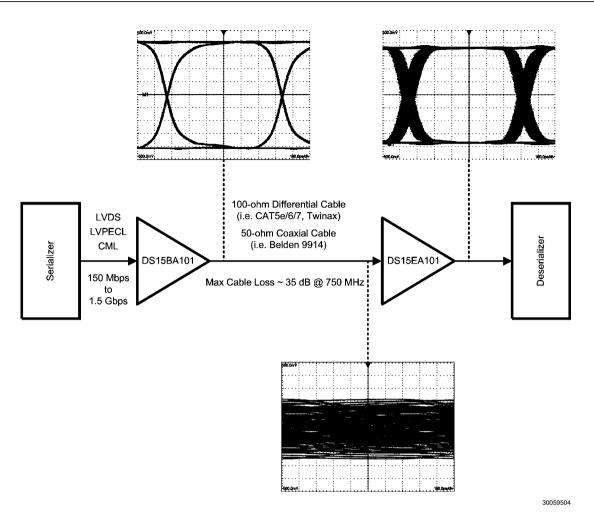

The cable extender chipset consists of the DS15BA101 and DS15EA101 devices. These are flexible devices that can be used with LVDS, LVPECL or CML signaling.

The DS15BA101 is a high speed differential buffer with adjustable output amplitude. It can be used for cable driving, level translation, signal buffering and signal repeating. It operates from DC to 1.5+ Gbps. In the application example, the serial line rate is roughly 1 Gbps and the DS15BA101 is well suited for the application. To set the optimal signal amplitude for the equalization, the buffering is required.

The companion device is the DS15EA101. It is an adaptive equalizer optimized for equalizing data transmitted over coaxial, twinax and twisted pair cables. The operating range for the equalizer is from 150 Mbps to 1.5+ Gbps. Due to the encoding of the FPD-Link II serial stream, the switching rate will remain above 150 Mbps even when sending flat field color data. The Equalizer automatically equalizes any cable length from zero meters to lengths that attenuate the signal by approximately 35 dB at 750 MHz.

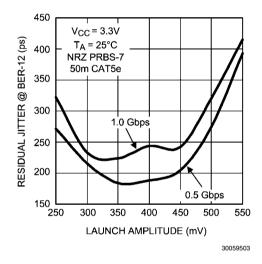

It is important to realize that the performance of the DS15EA101's automatic equalization circuitry is dependant on the signal amplitude at the transmitter or cable driver end of the cable – the launch amplitude. For 100  $\Omega$  differential cables (twinax or twisted pair cables), the optimal launch amplitude is  $\pm 400$  mV (800 mVp-p); and for  $50\Omega$  coaxial cables, it is also 800 mV (VOH-VOL). The energy detector circuitry in the DS15EA101 quantifies the energy of the incoming signal and feeds this analog information to the automatic equalization control circuitry which compares it with the assumed energy of the original signal and instructs the equalizer filter to apply certain amount of gain to the high frequency components of the signal based on the comparison. Any deviation from the optimal launch amplitude and as a result deviation in the signal energy from the assumed energy of the original signal in either direction will cause the equalizer filter to assert either excessive or insufficient amount of gain as illustrated in *Figure 3*. The DS15BA101 can provide signals with optimal launch amplitude for equalization of both, differential and single ended cables with minimal deviation over process, voltage and temperature. This is the reason the FPD-Link II SER Line Driver is buffered by the DS15BA101 in the application example.

FIGURE 3. DS15EA101 Output Residual Jitter as a Function of Launch Amplitude

Figure 3 shows how the launch amplitude affects the DS15EA101 output residual jitter when equalizing a 50 m CAT5e cable. It is clear that having a launch amplitude that is smaller or larger than the optimal amplitude (±400 mV +/- 10% for  $100\Omega$  differential cables) results in a higher output residual jitter. The data provided in Figure 3 was measured using a single twisted pair of the 50m CAT5e cable. The other twisted pairs in the cable were doubly terminated with  $100\Omega$  resistors to minimize reflections and crosstalk.

www.national.com 2

FIGURE 4. Line Driver Output, Equalizer Input, and Equalizer Output Eye Patterns

Figure 4 illustrates three important eye pattern locations in the example application. The serial signal is repeated and level shifted by the Cable Driver. The eye pattern at this location has optimal launch amplitude and very low jitter. After the losses due to the long twisted pair cable, the eye pattern is essentially closed. The signal amplitude is attenuated and jitter is excessive. The Equalizer provides gain that compensates for the cable losses and also repeats and level shifts the recovered eye pattern. Jitter is greatly reduced, and the signal swing is also recovered. The FPD-Link II DES receives this signal, performs the CDR operation, and provides the parallel output bus to the display.

# **Detailed Connection Diagram**

The FPD-Link II SER is typically loaded with a DC100  $\Omega$  load at the output and is AC coupled to the receiving device. The line is also terminated with a  $100\Omega$  termination as close to the DS15BA101 inputs as possible. This is done to minimize the resulting stub length. The AC coupling is used to isolate the offset voltage of the FPD-Link II driver (1.2V) from the DS15-BA101 input which is optimized for a higher input offset for the

lowest jitter performance. Coupling capacitors should be  $0.1\mu F$  or greater (i.e.  $1\mu F$ ), use standard values.

The DS15BA101 device requires an external resistor to VDD to set the optimal launch amplitude. A value of  $953\Omega$  is recommended for differential  $100\Omega$  applications. The DS15-BA101 outputs also require two  $50\Omega$  resistors pulled to VDD. All three resistors need to have 1% or better tolerance to ensure minimal variation of the launch amplitude.

The long reach cable is AC coupled at both ends to provide maximum isolation of the source and sink ends due to cable faults. The link is also compatible with AC coupling due to the encoding provided to the data by the FPD-Link II SER.

The DS15EA101 device requires an external filter cap as shown and recommended in the datasheet. Its differential outputs include internal  $50\Omega$  pull up resistors. Thus the common-mode offset is outside the range of the DS90UR124 inputs and this link needs to be AC coupled for compatibility reasons. Termination should be placed as close to the DES inputs to minimize any resulting stub lengths.

The detailed connection diagram is shown in Figure 5.

FIGURE 5. Extended Reach FPD-Link II SER/DES Connection Diagram

The link may be tested by either employing parallel BERT test equipment around this application or by using the on-chip BIST mode of the DS90UR241/124 chipset. The device is configured to output a PRBS stream that the DES detects and sets a status flag to indicate a PASS for error free transmission. Please refer to the DS90UR241/124 datasheet for details.

# **Design Considerations**

While factors such as pattern characteristics, SER/DES I/O characteristics, clock characteristics, connector and cable characteristics, power supply noise and system noise characteristics are important aspects of any design involving SER/DES devices, long reach applications require special attention to cable characteristics. There are three key twisted pair cable parameters that need to be considered when using TWP cable in long reach applications: cable attenuation, and for multi-pair applications: near-end crosstalk and pair-to-pair skew also need to be taken into account.

Cable attenuation is a measure of the decrease in signal strength along the length of a transmission line. Its two dominant parts are the skin effect and dielectric loss. While the skin effect is directly proportional to the square root of frequency, the dielectric loss is directly proportional to the frequency. Cable attenuation is the major jitter contributor when transmitting signals over long cables, thus the need for equalization.

0 -0.1 (Egg) SSOT NOIL -0.2 (AT7) (A

FIGURE 6. Twisted Pair Cable Attenuation

Figure 6 illustrates cable attenuation per unit length for various twisted pair cables. This data can be used to get an idea of what kind of attenuation signals will experience in a system. Let's say, a 50m CAT5e cable is employed in an FPD-Link II application, in a DVGA application operating at 40.5 MHz. The raw serial bit rate is 1.134 Gbps and corresponding Nyquist frequency is 567 MHz. Based on the data in Figure 6, CAT5e loss at 567 MHz is about -0.595 dB/m. A 50m CAT5e link would attenuate a sinusoidal 567 MHz signal by about -30 dB. If that sinusoidal signal had the amplitude of 400 mV, after 50m of CAT5e, its amplitude would be attenuated to 13 mV! Interestingly enough, amplitude of a 567 MHz square wave would roughly be the same if transmitted over a 50m CAT5e. This could be proven by performing a DFT (Discrete Fourier Transform) on the ideal square wave and attenuating each harmonic based on Figure 6 data.

For this application note, it is important to realize that signal amplitudes are very small when transmitted over long cables. Small signal amplitudes imply that even small amounts of noise may corrupt data. An equalizer, such as the DS15EA101 is a wide band, high gain, analog amplifier-filter that will boost high frequency components of an attenuated signal regardless of whether it has been corrupted or not; thus the importance of designing for low noise. See Application note AN-1347 for details about PCB Layout techniques that ensure well isolated, low noise environment for adaptive equalizers. This discussion also brings us to another important cable parameter, near end crosstalk (NEXT), a type of system noise that occurs when two or more signals are being transmitted over the same cable in a bi-directional manner.

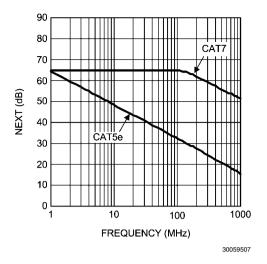

FIGURE 7. Twisted Pair Cable NEXT

Figure 7 illustrates NEXT for various category cables. For unshielded twisted pair (UTP) cables, the NEXT increases quickly with frequency and leaves little room for cable attenuation, therefore the maximum cable length for bi-directional transmission is much shorter verses unidirectional transmission such as in our example application. The cables with individually shielded or foiled twisted pairs (FTP) have much better NEXT performance and allow bidirectional transmission at frequencies beyond 1 GHz.

As a rule of thumb, signal to noise ratio or attenuation to crosstalk ratio (a cabling industry term), needs to be 15-20 dB if bi-directional transmission is desired. For example, if we go back to the DVGA application where we have an FPD-Link II application over a 50m CAT5e cable that attenuates a signal by 30 dB at 567 MHz and want to add a back channel using the same cable. The back channel would have to be a signal that does not couple to the primary channel by more than 45-50 dB assuming the same amplitude for both channels. A signal that would satisfy this requirement would have to have no significant frequency components above approximately 10

The pair-to-pair skew is a parameter that should not be overlooked when the timing relationship between signals being transmitted on the same twisted cable is critical. Novice CAT5e users find themselves surprised when they discover that pair-to-pair skew can be as large as 45 ns (typically 25 ns) per 100 meters (TIA/EIA-568-B.2). This is a high number of nanoseconds when dealing with signals running at hundreds of megabits per second. The FPD-Link II SER/DES in our example is not impacted by pair-to-pair skew as the entire bus is serialized to a single pair and thus can be dismissed.

# **How Far, How Fast?**

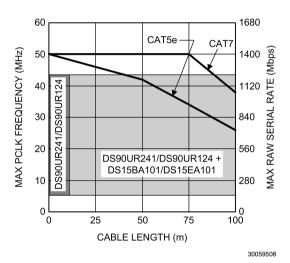

Next, bench data was collected to illustrate the operating boundaries of the part under the tested conditions. The recommended operating conditions for the DS90UR241/124 chipset is between TxCLKs (PCLK) of 5 to 43 MHz. The direct connection of SER to DES is typically limited to 10 meters or less. This is shown by the small operating box in *Figure 8*.

The lines on the chart were obtained from a bench test using external parallel BERT test equipment. It shows the operating margin obtained for two different types of twisted pair cable interconnects with the DS15BA101 and DS15EA101 devices employed for extending the length of the FPD-Link II serial link.

For the example DVGA application operating at 40.5 MHz, 50 meter lengths are possible with the higher loss CAT5e cabling. By using a lower loss cable with individually shielded twisted pairs (CAT7), the length is extended to almost 100 meters.

For a WVGA application, PCLK in the 30 MHz range, lengths of 75 to 100 meters are possible depending upon the cable selected.

FIGURE 8. How Far, How Fast – CAT5e and CAT7 Twisted Pair Cables

### Conclusion

Using the DS15BA101 & DS15EA101 Cable Driver and Equalizer allows for long reach cables to be used between the FPD-Link II SER/DES devices. The Equalizer provides up to 35 dB of gain to compensate for the cable losses. Armed with the adaptive equalizer's high gain capability and good design practices addressed in this application note, long reach FPD-Link II applications can be designed with ease. The long reach capability is useful for many industrial display applications where the Display is located at a great distance from the source.

### **Notes**

For more National Semiconductor product information and proven design tools, visit the following Web sites at:

| Products                       |                              | Design Support          |                                |

|--------------------------------|------------------------------|-------------------------|--------------------------------|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH                 | www.national.com/webench       |

| Audio                          | www.national.com/audio       | Analog University       | www.national.com/AU            |

| Clock Conditioners             | www.national.com/timing      | App Notes               | www.national.com/appnotes      |

| Data Converters                | www.national.com/adc         | Distributors            | www.national.com/contacts      |

| Displays                       | www.national.com/displays    | Green Compliance        | www.national.com/quality/green |

| Ethernet                       | www.national.com/ethernet    | Packaging               | www.national.com/packaging     |

| Interface                      | www.national.com/interface   | Quality and Reliability | www.national.com/quality       |

| LVDS                           | www.national.com/lvds        | Reference Designs       | www.national.com/refdesigns    |

| Power Management               | www.national.com/power       | Feedback                | www.national.com/feedback      |

| Switching Regulators           | www.national.com/switchers   |                         |                                |

| LDOs                           | www.national.com/ldo         |                         |                                |

| LED Lighting                   | www.national.com/led         |                         |                                |

| PowerWise                      | www.national.com/powerwise   |                         |                                |

| Serial Digital Interface (SDI) | www.national.com/sdi         |                         |                                |

| Temperature Sensors            | www.national.com/tempsensors |                         |                                |

| Wireless (PLL/VCO)             | www.national.com/wireless    |                         |                                |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2008 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: new.feedback@nsc.com

Tel: 1-800-272-9959

National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com German Tel: +49 (0) 180 5010 771 English Tel: +44 (0) 870 850 4288 National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com