# DP83848C PHYTER Single to DP83848J/M PHYTER Mini System Rollover Document

# **Purpose**

This is an informational document detailing points to be considered when migrating an existing 10/100 Mb/s Ethernet design using the National Semiconductor DP83848C PHYTER product to the smaller DP83848J or DP83848M products.

The DP83848C and DP83848J/M feature the following:

- Support 10/100 MII interface

- Operation over the commercial temperature range

- Compliant with IEEE 802.3 specification

This document compares differences including feature set, pin functions, package and pinout, and possible register operation differences between DP83848C and DP83848J/M to simplify end user setup and help ensure a better user experience. The impact to a design is dependant on features used and their implementation.

# 1.0 Required Changes

This section documents the hardware changes required to transition from the DP83848C to the DP83848J or DP83848M. The required changes for proper operation include package, pinout, bias and termination connections.

## 1.1 PACKAGE

The DP83848C is available in a 48 pin LQFP package. The DP83848J/M comes in a 40 pin LLP package. The differences in package between DP83848C and DP83848J/M are shown in *Table 1*. For more information on the DP83848 packages please visit

http://www.national.com/analog/packaging/

**TABLE 1. Packaging Differences**

|                 | DP83848C | DP83848J/M |  |  |

|-----------------|----------|------------|--|--|

| Package         | 48-LQFP  | LLP 40     |  |  |

| Footprint       | 7x7 mm   | 6x6 mm     |  |  |

| Package Drawing | VBH48A   | SQA40A     |  |  |

#### 1.2 PINOUT

The DP83848C has 48 pins while the DP83848J/M have a reduced pin count. The LLP package used on the DP83848J/M also has an exposed DAP pad. Please see Appendix A for the pin mapping between DP83848C and DP83848J/M, as well as pins not applicable in the DP83848J/M.

## 1.3 PCB MODIFICATION

This section describes the DP83848C circuit modifications required to use the DP83848J/M in a similar design.

## **1.3.1 PFBOUT**

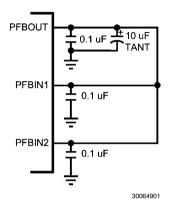

Both the DP83848C and DP83848J/M devices require similar connection of the Power Feedback circuit. Parallel capacitors

National Semiconductor Application Note 1854 Devin Seely September 3, 2008

(10uF Tantalum and 0.1uF ceramic) should be placed close to PFBOUT, the output of the regulator. PFBIN1 and PFBIN2 should be externally connected to PFBOUT as shown in *Figure 1*. A small 0.1uF capacitor should be placed close to the PFBIN1 and PFBIN2 pins. The pin assignment differences between the DP83848C and DP83848J/M are summarized in *Table 2*.

**FIGURE 1. PFBOUT Connection**

**TABLE 2. Power Feedback Connections**

| Signal Name | DP83848C | DP83848J/M |  |

|-------------|----------|------------|--|

| PFBOUT      | 23       | 19         |  |

| PFBIN1      | 18       | 16         |  |

| PFBIN2      | 37       | 30         |  |

#### 1.3.2 Bias Resistor

Internal circuitry biasing for the devices is accomplished in a similar manner. The only difference is the bias connection pin number.

The 4.87 kohm connects to pin 24 on the DP83848C and pin 20 on the DP83848J/M.

**TABLE 3. Bias Resistor Values**

|                     | DP83848C  | DP83848J/M |

|---------------------|-----------|------------|

| Bias Resistor Value | 4.87 kohm | 4.87 kohm  |

| Bias Pin            | 24        | 20         |

## 1.3.3 Termination and PMD Biasing

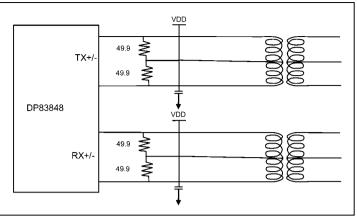

DP83848C and DP83848J/M PMD interface require two pair of 49.9 Ohm resistors, biased to VDD of the device. This matching of the termination resistors and common biasing between the receiver and transmitter accommodates the Auto-MDIX feature. Refer to *Figure 2* for a graphic explanation of this.

PHYTER® is a registered trademark of National Semiconductor.

3006490

FIGURE 2. DP83848 PMD Connections (Termination)

## 2.0 Potential Changes

The following section describes the specific changes that may be necessary to convert to a DP83848J/M based design.

#### 2.1 MII INTERFACE

The MII interface is used to connect the PHY to the MAC in 10/100 Mb/s systems. For a 5 V MII application, it is recommended to use 33 Ohm series resistors between the MAC and DP83848. The MII interface is a nibble-wide interface consisting of transmit data, receive data and control signals.

The transmit interface is comprised of the following signals:

- Transmit data bus, TXD[0:3] (pins 4, 5, 6 and 7 in DP83848J/M)

- Transmit enable signal, TX\_EN (pin 3 in DP83848J/M)

- Transmit clock, TX\_CLK (pin 2 in DP83848J/M) which runs at 2.5 MHz in 10 Mb/s mode and 25 MHz in 100 Mb/s mode

The receive interface is comprised of the following signals:

- Receive data bus, RXD[0:3] (pin 36, 37, 38 and 39 in DP83848J/M)

- Receive error signal, RX\_ER (pin 34 in DP83848J/M)

- Receive data valid, RX\_DV (pin 32 in DP83848J/M)

- Receive clock, RX\_CLK (pin 31 in DP83848J/M) for synchronous data transfer which runs at 2.5 MHz in 10 Mb/ s mode and 25 MHz in 100 Mb/s mode

Refer to Appendix A for a DP83848C to DP83848J/M pin mapping.

## 2.2 PHY ADDRESS

In a given system, multiple PHYs may be controlled by a single MII management interface. In order to support this, each PHY must have a unique address. DP83848 facilitates this with PHY address strap options.

In the DP83848, RXD[0:3] and COL are also used at powerup or reset time to set the PHY address. Pin COL has a weak internal pull-up and RXD[0:3] have weak internal pull-downs. Hence, the default PHY address setting in the DP83848C and DP83848J/M is 01h. To change the PHY address, from the default, add external 2.2 kohm pull-ups or pull-downs to the appropriate pin(s).

## 2.3 PHYSICAL LAYER ID REGISTER

The PHYsical Layer ID (PHYID) register allows system software to determine applicability of device specific software based on the vendor model number. The vendor model number is represented by bits 9 to 4 in PHYIDR2. The vendor model number in DP83848C is 001001b. For the DP83848J/M, the vendor model number is also 001001b.

TABLE 4. Register Change for Vendor Model Number

| Register<br>Address | Register<br>Name | Register<br>Description | Device       |                |

|---------------------|------------------|-------------------------|--------------|----------------|

| Hex                 |                  |                         | DP83848<br>C | DP83848<br>J/M |

| 03h                 | PHYIDR<br>2      | PHY ID 2                | 5C90h        | 5C90h          |

## 2.4 AUTO-NEGOTIATION AND LED PINS

DP83848C has 3 multifunction pins to configure the Auto-Negotiation capabilities. At power-up or reset time they strap the media mode and during normal operation they provide status LED indications. Pin 26 has multiple LED functions, Activity or Collision status, as well as enabling Auto-Negotiation. Pin 28 indicates link status and controls the advertised or forced mode (AN0) of DP83848C. Pin 27 indicates speed status and controls the advertised and forced mode (AN1) of DP83848C. Due to the reduced pin count in the DP83848J/M, the strapping options for Auto-Negotiation are reduced. For the DP83848J, the ability to strap a forced mode is not available. The DP83848M has an additional limitation of not being able to advertise 10 Base-T or 100 Base-TX only modes. The available Auto-Negotiation strapping modes are summarized in Table 6, Table 7, and Table 8. The full range of operating mode options are still available through register access.

## TABLE 5. DP83848 Pins for Auto-Negotiation and LED

| DP83848C Pin Number Auto-Negotiation Function |                                               | LED Function                  |

|-----------------------------------------------|-----------------------------------------------|-------------------------------|

| 26                                            | Auto-Negotiation enable                       | Activity and collision status |

| 27                                            | Controls the advertised and forced mode (AN1) | Speed status                  |

| 28                                            | Controls the advertised and forced mode (AN0) | Link status                   |

## TABLE 6. DP83848C Auto-Negotiation Modes

| AN_EN | AN0 | AN1 | Forced Mode                   |

|-------|-----|-----|-------------------------------|

| 0     | 0   | 0   | 10 Base-T, Half-Duplex        |

| 0     | 0   | 1   | 10 Base-T, Full-Duplex        |

| 0     | 1   | 0   | 100 Base-TX, Half-Duplex      |

| 0     | 1   | 1   | 100 Base-TX, Full-Duplex      |

| AN_EN | AN0 | AN1 | Advertised Mode               |

| 1     | 0   | 0   | 10 Base-T, Half/Full-Duplex   |

| 1     | 0   | 1   | 100 Base-TX, Half/Full-Duplex |

| 1     | 1   | 0   | 10 Base-T, Half-Duplex        |

|       |     |     | 100 Base-TX, Half-Duplex      |

| 1     | 1   | 1   | 10 Base-T, Half/Full-Duplex   |

|       |     |     | 100 Base-TX, Half/Full-Duplex |

## TABLE 7. DP83848J Auto-Negotiation Modes

| AN0 | AN1 | Advertised Mode               |  |

|-----|-----|-------------------------------|--|

| 0   | 0   | 10 Base-T, Half/Full-Duplex   |  |

| 0   | 1   | 100 Base-TX, Half/Full-Duplex |  |

| 1   | 0   | 10 Base-T, Half-Duplex        |  |

|     |     | 100 Base-TX, Half-Duplex      |  |

| 1   | 1   | 10 Base-T, Half/Full-Duplex   |  |

|     |     | 100 Base-TX, Half/Full-Duplex |  |

## TABLE 8. DP83848M Auto-Negotiation Modes

| AN0 | Advertised Mode               |  |

|-----|-------------------------------|--|

| 0   | 10 Base-T, Half-Duplex        |  |

|     | 100 Base-TX, Half-Duplex      |  |

| 1   | 10 Base-T, Half/Full-Duplex   |  |

|     | 100 Base-TX, Half/Full-Duplex |  |

# 3.0 Informational Changes

This section compares the features offered in the DP83848C and DP83848J/M and the changes required to implement them.

TABLE 9. DP83848C to DP83848J/M Feature Comparison

|                      | DP83848C   | DP83848J/M |

|----------------------|------------|------------|

| System Interfaces    |            |            |

| RMII                 | Yes        | Yes        |

| SNI                  | Yes        | No         |

| JTAG                 | No         | No         |

| Features             |            |            |

| Auto-MDIX            | Yes        | Yes        |

| Energy Detect        | Yes        | Yes        |

| LED Outputs          | 3          | 2 (J)      |

|                      |            | 1 (M)      |

| CLK-to-MAC Output    | Yes        | No (J)     |

|                      |            | Yes (M)    |

| Power Down/Interrupt | Yes        | No         |

| Temperature Range    | 0 to 70 °C | 0 to 70 °C |

| Power Consumption    |            |            |

| Active Power (Typ)   | 264mW      | 264mW      |

#### 3.1 RMII INTERFACE

The RMII interface can be used to connect the MAC to the PHY in 10/100 Mb/s systems using a reduced number of pins. By utilizing this feature, significant PCB space savings can be realized within the system, especially a design with a large number of physical layer devices.

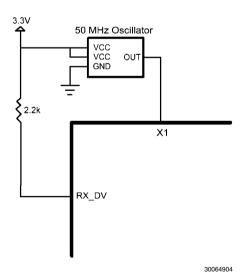

DP83848 uses an external 50 MHz clock (X1) as reference for both transmit and receive in the RMII mode. The 50 MHz is provided by an external oscillator. To enable RMII mode, RX\_DV should be pulled high using a 2.2 kohm resistor. Refer to Figure 3.

FIGURE 3. RMII Selection

#### 3.2 SNI MODE

DP83848C incorporates a 10 Mb/s Serial Network Interface (SNI) which allows a simple data interface for 10 Mb/s only system. While there is no defined standard for this interface, the interface is based on the earlier National Semiconductor 10 Mb/s physical layer devices. The DP83848J/M devices do not support SNI mode. The following pins are used in SNI mode:

- TX\_CLK

- TX\_EN

- TXD\_0

- RX\_CLK

- RXD\_0

- CRS

- COI

## 3.3 AUTO\_MDIX SETTING

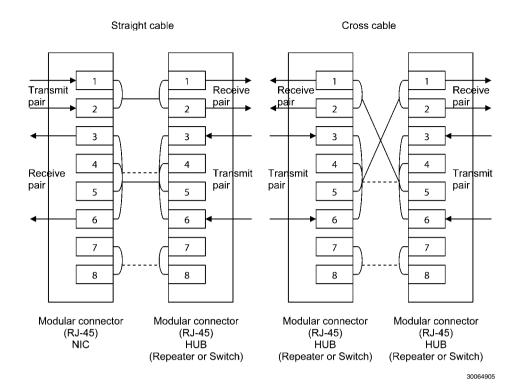

Auto-MDIX removes cabling complications and simplifies end customer applications by allowing either a straight or a crossover cable to be used without changing the system configuration. When enabled, this function utilizes Auto-Negotiation to determine the proper configuration for transmission and reception of data and subsequently selects the appropriate MDI pair for MDI/MDIX operation. Auto-MDIX is enabled by default in the DP83848C, DP83848J and DP83848M. To disable Auto-MDIX, RX\_ER should be pulled to ground using a 2.2 kohm resistor. See *Figure 4*.

FIGURE 4. Auto-MDIX Operation

5

## 3.4 ENERGY DETECT

Energy Detect facilitates flexible and automatic power management based on detection of a signal on the cable. This enables an application to use an absolute minimum amount of power over time. Energy Detect functionality is controlled via the Energy Detect Control Register (EDCR), address 1Dh. When Energy detect is enabled and there is no activity on the cable, the PHY will remain in a low power mode while monitoring the receive pair in the transmission line. Activity on the line will cause the PHY to return to the normal power mode.

## 3.5 CLK\_to\_MAC OUTPUT

DP83848C offers a clock output that may be routed directly to the MAC and act as the MAC reference clock, eliminating the need, and hence space and cost, of an additional MAC clock source. In MII mode, the clock output is 25 MHz and in

RMII mode, it is 50 MHz clock. The DP83848M has a 25MHz\_OUT pin, while the DP83848J does not.

## 3.6 POWER DOWN / INTERRUPT

DP83848C offers a separate, multifunction pin to allow the system to power down the device, or to indicate an interrupt. In Power\_Down mode, the PWR\_DOWN/INT pin (pin 7) may be asserted low to put the device in a power down state. In Interrupt mode, this pin is an open drain output and will be asserted low when an interrupt condition occurs, based on various criteria defined by the MISR and MICR registers. It is recommended to use an external pull-up resistor for proper operation of the interrupt function.

The interrupt functionality is not available in the DP83848J/M. The Power Down functionality is only available through register access in the DP83848J/M.

# Appendix A

TABLE 10. DP83848C & DP83848J/M Pin Map

| Signal Name          | DP83848C Pin # | DP83848J/M Pin # | Description                             |

|----------------------|----------------|------------------|-----------------------------------------|

| MII Interface Pins   | •              |                  | - · · · · · · · · · · · · · · · · · · · |

| MDC                  | 31             | 25               | MGMT DATA CLOCK                         |

| MDIO                 | 30             | 24               | MGMT DATA I/O                           |

| RXD0:3/PHYAD1:4      | 43,44,45,46    | 36,37,38,39      | MII RX DATA                             |

| RX_CLK               | 38             | 31               | MII RX CLOCK                            |

| RX_ER/MDIX_EN        | 41             | 34               | MII RX ERROR                            |

| RX_DV/MII_MODE       | 39             | 32               | MII RX DATA VALID                       |

| TXD0:3               | 3,4,5,6        | 4,5,6,7          | MII TX DATA                             |

| TX_CLK               | 1              | 2                | MII TX CLOCK                            |

| TX_EN                | 2              | 3                | MII TX ENABLE                           |

| COL/PHYAD0           | 42             | 35               | MII COL DETECT                          |

| CRS/LED_CFG          | 40             | 33               | MII CARRIER SENSE                       |

| PMD Interface Pins   |                |                  |                                         |

| RD-/+                | 13,14          | 11,12            | RX DATA                                 |

| TD-/+                | 16,17          | 14,15            | TX DATA                                 |

| Clock Interface Pins | ,              | ,                |                                         |

| X1                   | 34             | 28               | XTAL/OSC INPUT                          |

| X2                   | 33             | 27               | XTAL OUTPUT                             |

| LED Interface Pins   |                |                  | AINE COIL CI                            |

| LED_ACT/COL/AN_EN    | 26             | n/a              | COL LED STATUS                          |

| LED_ACT/COL/AN_EN    | 26             | n/a              | DUPLEX LED STATUS                       |

| LED_LINK/AN_0        | 28             | 22               | LINK LED STATUS                         |

| LED_SPEED/AN_1       | 27             | 21 (J)           | SPEED LED STATUS                        |

| LLD_3F LLD/AN_1      | 21             | n/a (M)          | SPEED EED STATOS                        |

| LED_ACT/COL/AN_EN    | 26             | n/a              | ACT LED STATUS                          |

| JTAG Interface Pins  |                | 11/4             | 7.01 225 0171100                        |

| TCK                  | 8              | n/a              | TEST CLOCK                              |

| TDO                  | 9              | n/a              | TEST DATA OUTPUT                        |

| TMS                  | 10             | n/a              | TEST MODE SELECT                        |

| TRST                 | 11             | n/a              | TEST RESET                              |

| TDI                  | 12             | n/a              | TEST DATA INPUT                         |

| Reset Function Pin   | 12             | 11/4             | TEOT DATA IN OT                         |

| RESET_N              | 29             | 23               | RESET                                   |

| Strap Pins           | 20             |                  | 1112021                                 |

| PHYAD0:4             | 42,43,44,45,46 | 35,36,37,38,39   | PHY ADDRESS                             |

| MDIX_EN/RX_ER        | 41             | 34               | AUTO MDIX ENABLE                        |

| MII_MODE/RX_DV       | 39             | 32               | MII MODE SELECT                         |

| SNI_MODE/TXD3        | 6              |                  | MII MODE SELECT                         |

| LED_CFG/CRS          | 40             |                  | LED CONFIGURATION                       |

| Bias Function Pins   | 40             | 20               | LLD CONTIGURATION                       |

|                      | 04             | 20               | DIAS DESISTOR COMMES                    |

| RBIAS                | 24             | 20               | BIAS RESISTOR CONNEC                    |

| Test Mode Pins       | 00             |                  | TEOT MODE OF SOT                        |

| AN_0/LED_LINK        | 28             | 22               | TEST MODE SELECT                        |

| AN_1/LED_SPEED       | 27             | 21 (J)           | TEST MODE SELECT                        |

| AN EN/LED ACT/COL    | 06             | n/a (M)          | TEST MODE SELECT                        |

| AN_EN/LED_ACT/COL    | 26             | n/a              | TEST MODE SELECT                        |

| Signal Name   | DP83848C Pin #  | DP83848J/M Pin # | Description         |

|---------------|-----------------|------------------|---------------------|

| 25MHz_OUT     | 25              | n/a (J)          | 25 MHz CLOCK OUTPUT |

|               |                 | 21 (M)           |                     |

| PWR_DOWN/INT  | 7               | n/a              | POWER DOWN/INT      |

| PFBIN1        | 18              | 16               | POWER FEEDBACK IN   |

| PFBIN2        | 37              | 30               | POWER FEEDBACK IN   |

| PFBOUT        | 23              | 19               | POWER FEEDBACK OUT  |

| Supply Pins   |                 |                  |                     |

| VDD           | 22,32,48        | 1,18,26          | 3.3 V               |

| GND           | 15,19,35,36,47  | 13,17,29,40      | GROUND              |

| Reserved Pins |                 |                  | •                   |

| RESERVED      | 8,9,10,11,12,20 | 8,9,10           | RESERVED            |

# **Appendix B**

This section covers differences between the registers in DP83848C and DP83848J/M applicable to software configuration of these devices.

## **Register Differences**

IEEE specified registers of National Semiconductor Physical Layer devices comply with the respective IEEE standards. Only vendor specific registers have functions that may vary from device to device. If no vendor specific registers are modified for operation in the system application, the devices will have similar operation. Specific functions of these vendor defined registers may be available in another register or possibly in a different bit within the same register location.

**TABLE 11. Register Bit Definitions**

| Reg Addr | Reg Name    | Register Description                            | Device                   |                     |

|----------|-------------|-------------------------------------------------|--------------------------|---------------------|

| Hex      |             |                                                 | DP83848C                 | DP83848J/M          |

| 10h      | PHYSTS      | PHY Status Register                             | Bit 7 MII Interrupt      | Bit 7 Reserved      |

| 11h      | MICR        | MII Interrupt Control Register                  | Bit 2 TINT               | Bit 2 Reserved      |

|          |             |                                                 | Bit 1 INTEN              | Bit 1 Reserved      |

|          |             |                                                 | Bit 0 INT_OE             | Bit 0 Reserved      |

| 12h      | MISR        | MII Interrupt Status Register                   | Bit 14 ED_INT            | Bit 14 Reserved     |

|          |             |                                                 | Bit 13 LINK_INT          | Bit 13 Reserved     |

|          |             |                                                 | Bit 12 SPD_INT           | Bit 12 Reserved     |

|          |             |                                                 | Bit 11 DUP_INT           | Bit 11 Reserved     |

|          |             |                                                 | Bit 10 ANC_INT           | Bit 10 Reserved     |

|          |             |                                                 | Bit 9 FHF_INT            | Bit 9 Reserved      |

|          |             |                                                 | Bit 8 RHF_INT            | Bit 8 Reserved      |

|          |             |                                                 | Bit 6 UNMSK_ED           | Bit 6 Reserved      |

|          |             |                                                 | Bit 5 UNMSK_LINK         | Bit 5 Reserved      |

|          |             |                                                 | Bit 4 UNMSK_JAB          | Bit 4 Reserved      |

|          |             |                                                 | Bit 3 UNMSK_RF           | Bit 3 Reserved      |

|          |             |                                                 | Bit 2 UNMSK_ANC          | Bit 2 Reserved      |

|          |             |                                                 | Bit 1 UNMSK_FHF          | Bit 1 Reserved      |

|          |             |                                                 | Bit 0 UNMSK_RHF          | Bit 0 Reserved      |

| 16h      | PCSR        | PCS Sub-Layer Configuration and Status Register | bit 12 BYP_4B5B          | Bit 12 Reserved     |

| 18h      | LEDCR       | LED Direct Control Register                     | Bit 5 DRV_SPDLED         | Bit 5 Reserved (M)  |

|          |             |                                                 | Bit 3 DRV_ACTLED         | Bit 3 Reserved      |

|          |             |                                                 | Bit 2 SPDLED             | Bit 2 Reserved (M)  |

|          |             |                                                 | Bit 0 ACTLED             | Bit 0 Reserved      |

| 19h      | PHYCR       | PHY Control Register                            | Bit 6 LEDCNFG[1]         | Bit 6 Reserved      |

| 1Ah      | 10BT_SERIAL | 10Base-T Status/Control                         | Bit 15 10BT_SERIAL       | Bit 15 Reserved     |

|          |             | Register                                        | Bit 14 REJECT 100 BASE T | Bit 14 Reserved     |

|          |             |                                                 | Bits 13:12 ERROR RANGE   | Bits 13:12 Reserved |

For additional information on these devices, please refer to the applicable datasheet(s).

DP83848C datasheet -

http://www.national.com/pf/DP/DP83848C.html

DP83848J datasheet -

http://www.national.com/pf/DP/DP83848J.html

DP83848M datasheet -

http://www.national.com/pf/DP/DP83848M.html

| Notes              |  |  |  |

|--------------------|--|--|--|

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

|                    |  |  |  |

| 9 www.national.com |  |  |  |

# **Notes**

For more National Semiconductor product information and proven design tools, visit the following Web sites at:

| Pr                             | oducts                       | Design Support          |                                |

|--------------------------------|------------------------------|-------------------------|--------------------------------|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH                 | www.national.com/webench       |

| Audio                          | www.national.com/audio       | Analog University       | www.national.com/AU            |

| Clock Conditioners             | www.national.com/timing      | App Notes               | www.national.com/appnotes      |

| Data Converters                | www.national.com/adc         | Distributors            | www.national.com/contacts      |

| Displays                       | www.national.com/displays    | Green Compliance        | www.national.com/quality/green |

| Ethernet                       | www.national.com/ethernet    | Packaging               | www.national.com/packaging     |

| Interface                      | www.national.com/interface   | Quality and Reliability | www.national.com/quality       |

| LVDS                           | www.national.com/lvds        | Reference Designs       | www.national.com/refdesigns    |

| Power Management               | www.national.com/power       | Feedback                | www.national.com/feedback      |

| Switching Regulators           | www.national.com/switchers   |                         |                                |

| LDOs                           | www.national.com/ldo         |                         |                                |

| LED Lighting                   | www.national.com/led         |                         |                                |

| PowerWise                      | www.national.com/powerwise   |                         |                                |

| Serial Digital Interface (SDI) | www.national.com/sdi         |                         |                                |

| Temperature Sensors            | www.national.com/tempsensors |                         |                                |

| Wireless (PLL/VCO)             | www.national.com/wireless    |                         |                                |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

## LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2008 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com German Tel: +49 (0) 180 5010 771 English Tel: +44 (0) 870 850 4288 National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com