# LM49270 Demonstration Board

National Semiconductor Application Note 1638 Vera Tsang May 2007

\_M49270 Demonstration Board

# **General Description**

The LM49270SQ demoboard is a fully assembled circuit board for use of evaluating the LM49270 Stereo Class D audio subsystem with OCL headphone amplifier, 3D enhancement, and headphone sense. The LM49270 operates from a 2.4V to 5.5V power supply. The filterless stereo class D amplifiers delivers 2.2W/channel into a  $4\Omega$  load with less than 10% THD+N with a 5V supply. The headphone amplifiers

feature National's Output Capacitor-less(OCL) architecture that eliminates the output coupling capacitors required by traditional headphone amplifiers. Additionally, the headphone amplifier can be configured as capacitively coupled loads.

The LM49270 features a 32 step volume control for the headphone and stereo output. The device mode select and volume are controlled through an  $I^2C$  compatible interface.

# **Bill of Materials**

| DESIGNATOR          | QUANTITY | DESCRIPTION                 |

|---------------------|----------|-----------------------------|

|                     |          | 100µF ± 10% 10V             |

| C1–C2               | 2        | C Case Tantalum Capacitors  |

|                     |          | AVX TPSC107K010R0075        |

|                     |          | 0.22µF ± 10% 16V X7R        |

| C4                  | 1        | 0603 Ceramic Capacitor      |

|                     |          | Murata GRM188R71C223KA01D   |

| 2.2µF ± 10% 16V X7R |          | 2.2µF ± 10% 16V X7R         |

| C5                  | 1        | 0805 Ceramic Capacitor      |

|                     |          | Murata GRM21BR71A225KA01L   |

|                     |          | 1μF ± 10% 16V 1206          |

| C6–C7               | 2        | Ceramic Capacitors          |

|                     |          | Murata GRM31MR71C105KA01L   |

| 10µF ± 10           |          | $10\mu F \pm 10\% \ 16V$    |

| C8                  | 1        | B Case Tantalum Capacitor   |

|                     |          | AVX TPSB106K016R0500        |

|                     |          | 1μF ± 10% 16V 0805          |

| C9–C12              | 4        | Ceramic Capacitors          |

|                     |          | Murata GRM21BR71C105KA01L   |

| B1                  | 1        | $4.7 k\Omega \pm 0.1\%$     |

|                     | •        | Panasonic-ECG ERA-3AEB472V  |

| R2 1                |          | 1kΩ ± 0.1%                  |

| 112                 |          | Panasonic-ECG ERA-3AEB102V  |

| R3                  | 1        | 100k $\Omega$ Potentiometer |

|                     |          | Digikey ST4B104CT           |

# AN-1638

# Connectors

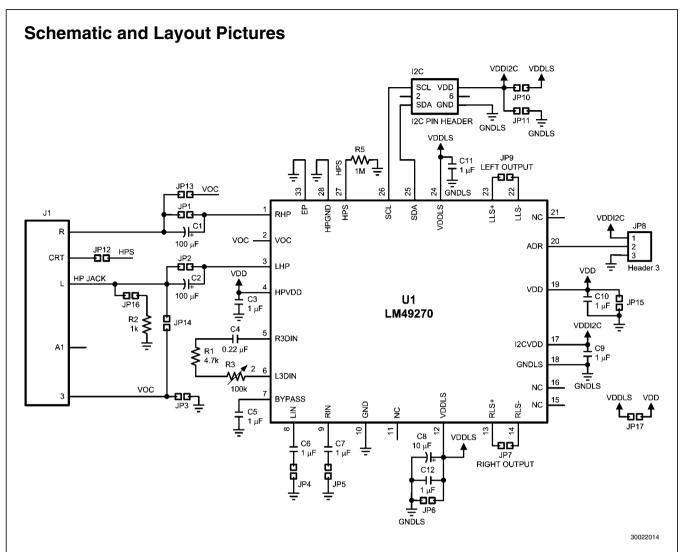

| DESIGNATOR | LABEL                             | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JP1, JP2   |                                   | These connectors are used to switch between CC or OCL mode.<br>If JP1 and JP3 are open, then the LM49270 is in CC mode.<br>If JP1 and JP3 are closed, then the LM49270 is in OCL mode.                                                                                                                                                                                                                            |

| JP3        | VOC                               | JP3 is used to ground the VOC pin of the LM49270.<br>In CC mode, JP3 should be closed, and the VOC amplifier is disabled.                                                                                                                                                                                                                                                                                         |

| JP4, JP5   | LIN, RIN                          | These connectors are used for connecting the input to the LM49270. LIN (JP4) is for left input, and RIN (JP5) is for right input.                                                                                                                                                                                                                                                                                 |

| JP6        | VDDLS                             | This connector is for the loudspeaker power supply connection. Apply an external power supply's positive voltage to the pin labeled VDDLS and the ground source to the pin labeled GND.                                                                                                                                                                                                                           |

| JP7, JP9   | RIGHT<br>SPEAKER, LEFT<br>SPEAKER | These connectors are for the right speaker output (JP7) and left speaker output (JP9).                                                                                                                                                                                                                                                                                                                            |

| JP8        | VDDI2C/ADR/<br>GND                | There are three pins on this connector, VDDI2C, ADR, and GND. It is used to set the LM49270 address. To set the ADR bit to 1, close VDDI2C and ADR. To set the ADR bit to 0, close GND and ADR.                                                                                                                                                                                                                   |

| JP10       |                                   | This connector should be closed when the user wants to use the VDDLS as the VDD source for the I2CVDD.                                                                                                                                                                                                                                                                                                            |

| JP11       | VDDI2C                            | This connector can be used to connect to a VDD source if the user wants to power the VDDI2C externally.                                                                                                                                                                                                                                                                                                           |

| JP12       | HPS                               | This connector is connected to the headphone sense pin of the part and<br>the headphone jack.<br>If JP12 is closed, then the headphone sense function works as designed<br>with a headphone jack.<br>If JP12 is open, then the user does not need a headphone jack to test the<br>function of the HPS. To set to HP mode, set the right pin of JP12 to low.<br>To set to speaker mode, set the right pin to high. |

| JP13, JP14 | RHP, LHP                          | These connectors are for the right headphone output (JP13) and the left headphone output (JP14).                                                                                                                                                                                                                                                                                                                  |

| JP15       | VDD                               | This connector provides the power supply connection. Apply an external power supply's positive voltage to the pin labeled VDD and the ground source to the pin labeled GND.                                                                                                                                                                                                                                       |

| JP16       |                                   | This connector is used to short the LHP to a pull down resistor.<br>In CC mode, JP16 should be closed.<br>In OCL mode, JP16 should be open.                                                                                                                                                                                                                                                                       |

| JP17       |                                   | This connector is used to short VDD and VDDLS together. If the user wanted to use only one power supply, then closing JP17 will allow the power supply to be connected to JP15 or JP6 only.                                                                                                                                                                                                                       |

# **Quick Start - in CC Mode**

1) Connect a shunt across the ADR and GND pins of jumper JP8. (I<sup>2</sup>C address bit = 0)

2) Connect a shunt across jumper JP3 (VOC = GND, Capacitor Coupled (CC) headphone mode).

3) Connect a shunt across jumper JP16 (for Capacitor Coupled (CC) headphone mode).

4) Connect a shunt across jumper JP12 to use the headphone sense function.

5) Connect an  $8\Omega$  speaker across jumper JP7 (Right Speaker output).

6) Connect an  $8\Omega$  speaker across jumper JP9 (Left Speaker output).

7) Connect a headphone to jack J1 (headphone jack).

8) Connect the 3.3V power supply to the VDD pin of jumper JP15 and the VDDLS pin of jumper JP6, and the power supply ground terminal to the GND pin of jumper JP15 and jumper JP6.

Connect the audio source to JP4 (left input) and JP5 (right input).

10) Connect I<sup>2</sup>C from PC to I<sup>2</sup>C Interface jumper.

11) Open LM49270 I2C control software.

12) Turn on power supply and audio source.

13) In the LM49270 I<sup>2</sup>C control panel, select "C-CUPL" in HEADPHONE OUTPUT COUPLING, and select CHIP POW-ER-ON mode "ON" to enable the device.

14) Adjust the volume controls to change the speaker and headphone volumes.

15) To enable the speakers, disconnect the headphone from jack J1.

# **Board Connections**

#### POWER CONNECTIONS

Power Connections The LM49270 demoboard offers separate connections for the speaker amplifier and headphone amplifier power supplies. The separate power supplies allow the speakers to operate at a higher voltage for maximum headroom, while the headphones operate at a lower voltage, improving power dissipation. Connect the headphone amplifier power supply to the VDD pin and the power supply ground to the GND pin of jumper JP15. Connect the speaker amplifier power supply to the VDDLS pin and the power supply ground to the GND pin of JP6. As for the I<sup>2</sup>CV<sub>DD</sub>, if powered from JP11, it allows the I<sup>2</sup>C portion of the LM49270 to interface with lower voltage digital controllers.

#### AUDIO INPUT CONNECTIONS

The left and right channel inputs of the LM49270 demoboard is configured for single-ended sources. Connect a left channel input source to the LIN pin and GND pin of JP4 and connect the a right channel input source to the RIN pin and GND pin of JP5.

#### AUDIO OUTPUT CONNECTIONS

Jumpers JP9 and JP7 are the connections for the left and right channel speakers output respectively. The jack, J1 is a 3.5mm stereo headphone jack with a headphone sense pin.

### **Jumper Selection**

In CC mode, install a shunt across jumper JP3 and jumper JP16. In OCL mode, install a shunt across jumper JP1 and jumper JP2.

#### I<sup>2</sup>C Interface

The LM49270 is controlled through an I<sup>2</sup>C compatible serial interface. The LM49270 evaluation software provides an easy

to use graphical user interface (Figure 1). Each button corresponds to bits in an I<sup>2</sup>C command byte. See the LM49270 data sheet for detailed I<sup>2</sup>C information.

| M49270 Audio Program v1.2                                     |              |            |             |

|---------------------------------------------------------------|--------------|------------|-------------|

| National<br>Semiconductor<br>The Sight & Sound of Information | C ON OFF     | CHIP POWER | ON<br>© OFF |

| EADPHONE OUTPUT COUPLING                                      | HEADPHONE 3D | C 1        | BIT         |

| DLUME CONTROLS                                                |              | - 6.0 dB   | DEFAUL      |

FIGURE 1. Evaluation Software Interface

#### **CHIP POWER - ON**

The Chip Power-On button enables or disables the entire device. The device will not output any audio if the Chip Power-On is set to "Off."

#### I<sup>2</sup>C ADDRESS BIT

The selection of this bit should correspond to the user's selection on jumper JP8. If the ADR pin is set to GND, then the I<sup>2</sup>C Address Bit should be set to '0'. If the ADR pin is set to VDDI2C, then the I<sup>2</sup>C Address Bit should be set to '1'.

#### LOUDSPEAKER 3D, HEADPHONE 3D

The Loudspeaker 3D and Headphone 3D button enables 3D sound enhancement for loudspeaker and Headphone, re-

spectively. By setting it to "ON" turns on 3D and allows the user to increase or decrease the 3D effect on the demoboard by changing the value of the potentiometer in the external RC network of the LM49270.

#### VOLUME CONTROL

The LM49270 headphone and speaker channels feature separate volume controls. The loudspeaker volume has a range of -49dB to 30dB and the headphone has a range of -59dB to 18dB, each with 32 steps.

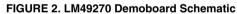

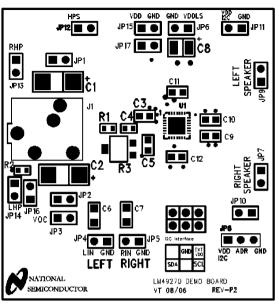

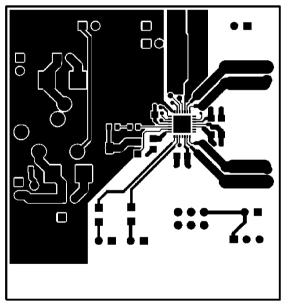

# **Demonstration Board PCB Layout**

30022013

FIGURE 3. Top Silkscreen Layer

30022009

FIGURE 4. Top Layer

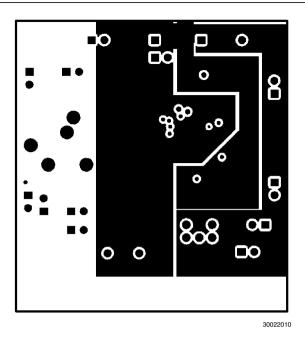

FIGURE 5. Mid Layer 1

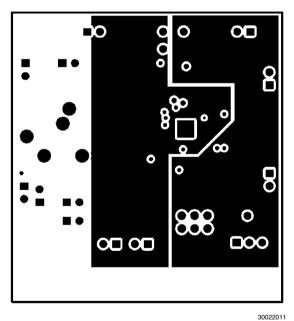

FIGURE 6. Mid Layer 2

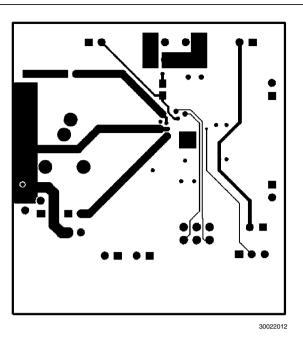

FIGURE 7. Bottom Layer

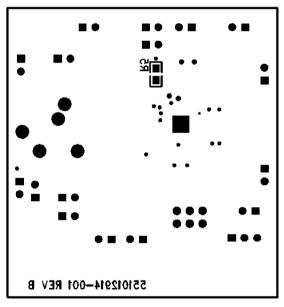

30022008

FIGURE 8. Bottom Silkscreen

| Revision History |     |          |                  |  |  |  |

|------------------|-----|----------|------------------|--|--|--|

|                  | Rev | Date     | Description      |  |  |  |

|                  | 1.0 | 05/24/07 | Initial release. |  |  |  |

Notes

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2007 National Semiconductor Corporation

For the most current product information visit us at www.national.com

N-1638

1

National Semiconductor Americas Customer Support Center Email: new.feedback@nsc.com Tei: 1-800-272-9959

National Semiconductor Europe

Customer Support Center

Fax: +49 (0) 180-530-85-86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +49 (0) 87 024 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560